De programmeur heeft de beschikking over adresruimte, alleen beperkt door de adresbusbreedte, ongeacht echte capaciteit werkgeheugen computer en de hoeveelheid geheugen die wordt gebruikt door andere programma's die parallel worden verwerkt op een computer met meerdere programma's.

Virtueel geheugen, dat de programmeur de mogelijkheid biedt om toegang te krijgen tot een zeer grote hoeveelheid aaneengesloten adresruimte die hem exclusief ter beschikking staat, heeft de gebruikelijke eigenschappen: byte-adressering, toegangstijd vergelijkbaar met de toegangstijd tot RAM.

In alle fasen van de programmavoorbereiding, inclusief het laden in geheugen, programma verschijnt in virtuele adressen, en alleen bij het uitvoeren van een machineopdracht virtuele adressen worden omgezet in fysieke. Voor elk programma dat wordt uitgevoerd in de multiprogrammamodus, zijn eigen programma virtueel geheugen. Elk programma gebruikt hetzelfde virtuele adressen van nul tot de grootste in een bepaalde architectuur.

Bekeren virtuele adressen in fysiek fysiek en virtueel geheugen zijn verdeeld in blokken met een vaste lengte, genaamd Pagina's. De volumes van virtuele en fysieke pagina's zijn hetzelfde. Virtueel en fysiek geheugen zijn genummerd. Pagina's die ontbreken in het fysieke geheugen, worden meestal opgeslagen in het externe geheugen. Vaste maat van alle pagina's kunt u elke gewenste virtuele pagina in elke fysieke pagina laden.

Zoals hierboven opgemerkt, is bij een wisselbare geheugenrepresentatie de virtuele ( logisch) adres vertegenwoordigt het getal virtuele pagina en de offset op die pagina. Op zijn beurt , fysiek adres- dit nummer fysieke pagina en de verplaatsing daarin.

Regels voor het converteren van virtuele paginanummers naar nummers fysieke pagina's meestal in tabelvorm weergegeven pagina conversie. Dergelijke tabellen worden gevormd door het geheugenbeheersysteem en worden elke keer gewijzigd wanneer geheugen opnieuw wordt toegewezen. besturingssysteem bewaakt voortdurend de status van de virtuele pagina's van een bepaald programma en bepaalt of het zich in het RAM bevindt, en zo ja, op welke specifieke locatie. Applicatieprogramma's hebben geen betrekking op het proces en kunnen door iedereen worden gebruikt adresruimte. De processor genereert automatisch een speciaal geval van niet-aanwezigheid wanneer een programma toegang krijgt tot een pagina die zich niet in het fysieke geheugen bevindt. Bij het afhandelen van dit speciale geval laadt het besturingssysteem de gevraagde pagina uit het externe geheugen, waarbij optioneel een andere pagina naar schijf wordt verzonden (swapproces).

De vertaling van virtuele adressen naar fysieke adressen wordt geïllustreerd in Fig. 3.12.

Rijst. 3.12.

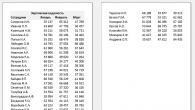

Laten we eens kijken naar een voorbeeld van adresvertaling virtuele pagina naar fysieke pagina. Laat de computer gebruiken adresruimte, waarbij paging plaatsvindt met een volume van V pagina's = 1I, en RAM V RAM = 3 pagina's heeft. Laat vier programma's tegelijkertijd draaien op een computer met het volgende aantal pagina's: VA = 2, VB = 1, VC = 3, V D = 2. Het schakelen tussen programma's vindt plaats na een kwantumtijd t k = 1. doorlooptijd elke pagina van welk programma dan ook is t = 2t k . Wij zijn van mening dat programmapagina's indien nodig en wanneer mogelijk in het RAM worden geladen. vrije gebieden RAM. Als al het geheugen bezet is, dan nieuwe pagina vervangt degene die het langst niet is gebruikt.

Onder dergelijke omstandigheden laadt het RAM de tabel en tabellen pagina conversie voor elk programma wordt het formulier weergegeven in de tabel. 3.2.

In de RAM-distributietabel worden de aantallen pagina's die actief zijn in een bepaalde cyclus gemarkeerd. In tabellen pagina conversie Streepjes geven situaties aan waarin dit voorkomt virtuele pagina ontbreekt in het RAM-geheugen.

| Bladzijde | Dus jij | |||||||||||||||

| 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 | 16 | |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Dynamische geheugentoewijzing | ||||||||||||||||

| RAM-geheugen 0 | JSC | JSC | JSC | DOEN | DOEN | DOEN | CO | CO | CO | C1 | C1 | C1 | C1 | C1 | C1 | C1 |

| 1 | B0 | B0 | B0 | A0 | A0 | A0 | D0 | D0 | D0 | D1 | D1 | D1 | D1 | D1 | D1 | |

| 2 | C0 | C0 | C0 | B0 | B0 | B0 | A1 | A1 | A1 | A1 | A1 | A1 | C2 | C2 | ||

| Tafel pagina conversie voor programma A | ||||||||||||||||

| Een 0 | 0 | 0 | - | - | 1 | 1 | 1 | - | - | - | - | - | - | - | - | - |

| 1 | - | - | - | - | - | - | - | - | 2 | 2 | 2 | 2 | 2 | 2 | - | - |

| Tafel pagina conversie voor programma B | ||||||||||||||||

| B0 | - | 1 | 1 | 1 | - | 2 | 2 | 2 | - | - | - | - | - | - | - | - |

| Tafel pagina conversie voor programma C | ||||||||||||||||

| Vanaf 0 | - | - | 2 | 2 | 2 | - | 0 | 0 | 0 | - | - | - | - | - | - | - |

| 1 | - | - | - | - | - | - | - | - | - | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 2 | - | - | - | - | - | - | - | - | - | - | - | - | - | - | 2 | 2 |

| Tafel pagina conversie voor programma D | ||||||||||||||||

| D0 | - | - | - | 0 | 0 | 0 | - | 1 | 1 | 1 | - | - | - | - | - | - |

| 1 | - | - | - | - | - | - | - | - | - | - | 1 | 1 | 1 | 1 | 1 | 1 |

Als elke pagina een volume van 1000 adresseerbare cellen heeft, wordt bijvoorbeeld in cyclus 9 toegang tot virtueel adres 1100 programma A ( virtuele pagina 1, de pagina-offset is 100) resulteert in een oproep op fysiek adres 2100 ( fysieke pagina 2, gecompenseerd in fysieke pagina hetzelfde als in de virtuele, dat wil zeggen 100).

Laten we nu eens kijken naar de toepassing hiervan algemene principes vertaling van paginaadressen V microprocessor met IA-32-architectuur met een paginagrootte van 4 KB.

Basis pagina conversie serveert 32-bits lineair adres, verkregen in de fase van segmenttransformatie logisch adres. Paginaconversie uitgevoerd wanneer de PG-bitwaarde = 1 in het besturingsregister CRO.

In dit geval de hoogste 20 bits lineair adres vertegenwoordigen eigenlijk een getal virtuele pagina. Echter met een directe conversie in één stap van dit nummer naar het nummer fysieke pagina een tabel van 2 20 elementen, elk 4 bytes lang (20-bits paginanummer plus enkele Extra informatie), d.w.z. 4 MB. In een multiprogrammeeromgeving kan een dergelijke tabel voor elke taak nodig zijn. Deze tabel moet permanent in het RAM worden opgeslagen om de formatietijd niet aanzienlijk te verlengen fysiek adres. Voor deze doeleinden zal het noodzakelijk zijn om voortdurend een aanzienlijk deel van de RAM-capaciteit te reserveren, wat praktisch onmogelijk was in de fase van het verschijnen van de eerste MP-gebaseerde computers met de IA-32-architectuur.

In plaats daarvan gebruikt de microprocessor een tweetraps vertaling van paginaadressen. De hoofdpagina, genaamd paginatabelmap(KTS), bevat 1024 32-bits paginatabel directory-element(ECTS - PDE-paginamapinvoer). Elk van hen richt zich tot een ondergeschikte pagina tabel(TS), dat wil zeggen dat er in totaal maximaal 1024 is toegestaan ondergeschikte tabellen Pagina's. Elke paginatabel bevat 1024 32-bits paginatabelelement(ETS - PTE-pagina tabel binnenkomst), die elk een fysieke pagina adresseren. Dus het totaal aantal adressen fysieke pagina's is gelijk aan 2 20, dat wil zeggen, alles is virtueel adresruimte(4 KB * 2 20 elementen = 2 32 bytes). Elke tabel beslaat 1024 * 4 = 4 KB, dat wil zeggen precies 1 pagina. Totale grootte van de gebruikte tafels pagina conversie, is niet afgenomen, maar zelfs licht gestegen als gevolg van het gebruik van de paginatabeldirectory. Ten eerste kan deze omvang echter bijna altijd in een systeem aanzienlijk worden verkleind vanwege het feit dat sommige lineaire adressen zal nooit worden gevormd (en deze informatie wordt gegeven descriptortabellen segmenten) en hoeft u er geen paginatabel voor te maken. En ten tweede alleen de paginatabel directory en paginatabel momenteel actief programma. Rest pagina tabellen kan tijdelijk worden opgeslagen in een extern geheugen.

Rijst. 3.13.

De conversie van een lineair adres naar een fysiek adres heeft dus de vorm getoond in Fig. 3.13.

Bovenste 20 cijfers lineair adres worden opgesplitst in twee 10-bits velden: veld paginatabel catalogusartikelnummers en veld paginatabelelementnummers. Sinds paginatabelmap, en elk pagina tabel bezetten precies 1 pagina en zijn uitgelijnd met de paginagrens, en vervolgens met de onderste 12 bits ervan basis adres gelijk zijn aan nul, en om ze te bepalen fysiek adres Een veld van 20 bits is voldoende.

Voor paginatabelmap het 20-bits adres is binnen controle register CR3. De CTS bevindt zich permanent in het geheugen en neemt niet deel aan het wisselen.

Bovenste 20 cijfers fysiek adres pagina tabellen worden uit het ETS gehaald. De structuren van het CTS-element en het TS-element zijn vergelijkbaar (Fig. 3.14).

Rijst. 3.14.

De meest significante 20 bits van het element geven het basisadres pagina tabellen(in ECTS) of fysieke pagina(in ETS). De P-, A-, R/W- en U/S-bits hebben bepaalde overeenkomsten met die van de segmentdescriptor; andere bits hebben specifieke doeleinden.

Paginageheugen- een methode voor het organiseren van virtueel geheugen, waarbij de eenheid voor het toewijzen van virtuele adressen aan fysieke adressen een regio is constante grootte(zogenaamde bladzijde). De typische paginagrootte is 4096 bytes, tot 128 KB voor sommige architecturen.

Ondersteuning voor deze modus is aanwezig in de meeste 32-bits en 64-bits processors. Deze modus is klassiek voor bijna alle moderne besturingssystemen, inclusief Windows en de UNIX-familie. Breed gebruik Deze modus begon met de VAX-processor en het VMS-besturingssysteem vanaf eind jaren zeventig (volgens sommige bronnen de eerste implementatie). In de x86-familie verscheen ondersteuning met de 386-generatie, wat tevens de eerste 32-bit-generatie is.

Problemen die moeten worden opgelost [ | ]

Concepten [ | ]

Adres gebruikt in machine code, dat wil zeggen de pointerwaarde, wordt een “virtueel adres” genoemd.

Het adres dat door de processor aan de bus wordt toegewezen, wordt een “lineair adres” genoemd (dat later wordt omgezet in een fysiek adres).

Een paginatabelitem bevat doorgaans de volgende informatie:

Het aantal records in één tabel is beperkt en afhankelijk van de recordgrootte en paginagrootte. Er wordt gebruik gemaakt van een indeling van tabellen op meerdere niveaus, vaak 2 of 3 niveaus, soms 4 niveaus (voor 64-bits architecturen).

In het geval van 2 niveaus wordt een pagina "directory" gebruikt, waarin gegevens zijn opgeslagen die verwijzen naar de fysieke adressen van de paginatabellen. Tabellen bevatten records die naar pagina's met gegevens verwijzen.

Bij gebruik van een organisatie op 3 niveaus wordt een supermap toegevoegd waarin vermeldingen worden opgeslagen die naar meerdere mappen verwijzen.

De hoge bits van het virtuele adres geven het invoernummer in de directory aan, de middelste bits geven het invoernummer in de tabel aan, de lage bits (het adres op de pagina) gaan zonder vertaling naar het fysieke adres.

Het formaat van tabelgegevens, hun grootte, paginagrootte en tabelorganisatie zijn afhankelijk van het type processor en soms van de bedieningsmodus.

Historisch gezien gebruikte x86 32-bits PTE's, 32-bits virtuele adressen, pagina's van 4 KB, 1024 tabelvermeldingen en tabellen met twee niveaus. De belangrijkste 10 bits van het virtuele adres zijn het itemnummer in de directory, de volgende 10 zijn het itemnummer in de tabel, de onderste 12 zijn het adres op de pagina.

Vanaf de Pentium Pro ondersteunt de processor 4 MB pagina's. Om ervoor te zorgen dat het systeem en de programma's die erop draaien pagina's van dit formaat kunnen gebruiken, moet de paginatechnologie van 4 MB (hugepages) echter correct zijn ingeschakeld en moet de toepassing zijn geconfigureerd om pagina's van dit formaat te gebruiken.

Op de x86_64-architectuur is het mogelijk om pagina's van 4 kilobytes (4096 bytes), 2 megabytes en (op sommige AMD64's) 1 gigabyte te gebruiken.

Als een geheugentoegang niet via de TLB kan worden vertaald, heeft de processormicrocode toegang tot de paginatabellen en probeert van daaruit de PTE in de TLB te laden. Als er na een dergelijke poging problemen blijven bestaan, voert de processor een speciale interrupt uit, genaamd “page error”. De handler voor deze interrupt bevindt zich in het subsysteem virtueel geheugen OS-kernels.

Sommige processors (MIPS) hebben geen microcode voor toegang tot tabellen en genereren onmiddellijk een paginafout nadat een TLB-opzoekopdracht mislukt, waardoor de toegang tot de tabel en de interpretatie aan de paginafouthandler worden overgelaten. Hiermee wordt de vereiste verwijderd dat paginatabellen op hardwareniveau moeten voldoen aan een hardgecodeerd formaat.

Redenen voor het mislukken van de pagina ( pagina fout):

- er is geen tabel die deze regio weergeeft,

- PTE heeft niet de vlag 'pagina weergegeven' ingesteld,

- een poging om vanuit de gebruikersmodus toegang te krijgen tot een “alleen kernel”-pagina,

- proberen naar een alleen-lezen pagina te schrijven,

- een poging om code uit te voeren vanaf de pagina “uitvoering verboden”.

De kernelfouthandler kan worden geladen gewenste pagina vanuit een bestand of vanuit het swapgebied (zie swap), kan een beschrijfbare, alleen-lezen kopie van de pagina maken, en kan in dit proces ook een uitzondering genereren (in UNIX-termen: het SIGSEGV-signaal).

Elk proces heeft zijn eigen proces eigen setje pagina tabellen. Het paginadirectoryregister wordt telkens opnieuw geladen wanneer een procescontext verandert. Het is ook noodzakelijk om het deel van de TLB dat op dit proces van toepassing is, opnieuw in te stellen.

In de meeste gevallen wordt de OS-kernel in dezelfde adresruimte geplaatst als de processen, en wordt de bovenste 1-2 gigabyte van de 32-bits adresruimte van elk proces daarvoor gereserveerd. Dit wordt gedaan om te voorkomen dat er tussen paginatabellen wordt gewisseld bij het binnenkomen en verlaten van de kernel. Kernelpagina's zijn gemarkeerd als ontoegankelijk voor code in de gebruikersmodus.

Het geheugen van de kernelregio is vaak precies hetzelfde voor alle processen, maar sommige subregio's van de kernelregio (bijvoorbeeld de Windows-regio waar het grafische subsysteem en het videostuurprogramma zich bevinden) kunnen verschillend zijn voor verschillende groepen processen (sessies).

Omdat het kernelgeheugen voor alle processen hetzelfde is, hoeven de bijbehorende TLB's na een proceswisseling niet opnieuw te worden geladen. Voor deze optimalisatie ondersteunt x86 de "algemene" vlag van de PTE.

Geheugen toegewezen bestanden[ | ]

De paginafouthandler in de kernel kan lezen deze pagina van bestand.

Dit leidt tot de mogelijkheid van eenvoudige implementatie van in het geheugen toegewezen bestanden. Conceptueel gezien is dit hetzelfde als het toewijzen van geheugen en het lezen van een sectie van een bestand daarin, met het verschil dat het lezen impliciet “op aanvraag” wordt uitgevoerd, wat tot uiting komt in een paginafout bij het proberen er toegang toe te krijgen.

Het tweede voordeel van deze aanpak is - in het geval van alleen-lezen mapping - de verdeling van hetzelfde fysieke geheugen over alle processen die een bepaald bestand weergeven (elk proces heeft zijn eigen toegewezen geheugen).

Het derde voordeel is de mogelijkheid om sommige toegewezen pagina's te 'vergeten' (weg te gooien) zonder ze in het wisselgebied te dumpen dat nodig is voor toegewezen geheugen. Als de pagina weer nodig is, kan deze snel weer vanuit het bestand worden geladen.

Het vierde voordeel is dat de schijfcache in deze modus niet wordt gebruikt, wat besparingen betekent bij het kopiëren van gegevens uit de cache naar de gevraagde regio. De voordelen van de schijfcache, die kleine bewerkingen optimaliseert, evenals het herhaaldelijk lezen van dezelfde gegevens, verdwijnen volledig bij het lezen van hele pagina's en vooral hun groepen, terwijl het nadeel van verplicht onnodig kopiëren blijft bestaan.

Geheugentoegewezen bestanden worden zowel in Windows OS als in OS gebruikt UNIX-familie, om uitvoerbare modules te laden en dynamische bibliotheken. Ze worden ook gebruikt door het GNU grep-hulpprogramma om een binnenkomend bestand te lezen, en om lettertypen in een aantal grafische subsystemen te laden.

Virtueel geheugen pagina's en segmenteren[ | ]

Een groot voordeel van gewisseld virtueel geheugen vergeleken met gesegmenteerd geheugen is de afwezigheid van ‘dichtbij’ en ‘veraf’-aanwijzers.

De aanwezigheid van dergelijke concepten in het programmeren vermindert de toepasbaarheid van pointer-rekenkunde en leidt tot enorme problemen met de overdraagbaarheid van code naar/van dergelijke architecturen. Een aanzienlijk deel van de software is bijvoorbeeld voorzien van open source werd oorspronkelijk ontwikkeld voor segmentloze 32-bits platforms met pagina geheugen en kan niet worden overgedragen naar segmentarchitecturen zonder ingrijpende aanpassingen.

Bovendien hebben segmentarchitecturen het ernstige SS != DS-probleem, dat begin jaren negentig algemeen bekend was bij het programmeren voor 16-bits Windows-versies. Dit probleem leidt tot problemen bij de implementatie van dynamische bibliotheken, omdat ze hun eigen DS en SS van het huidige proces hebben, wat leidt tot de onmogelijkheid om er 'dichtbij'-aanwijzers in te gebruiken. Voor het hebben van een eigen DS in de bibliotheken zijn ook installatieprogramma's vereist juiste waarde DS-patches (MakeProcInstance) voor terugbellen van de bibliotheek naar de oproepende applicatie.

Virtueel geheugen en schijfcache[ | ]

Hoofd artikel:(Engels)Ondersteuning voor in het geheugen toegewezen bestanden vereist dat de besturingssysteemkernel de structuur ondersteunt: een reeks fysieke pagina's die segmenten bevatten van dit bestand" Het in kaart brengen van een bestand in het geheugen gebeurt door tabelitems te vullen met koppelingen naar pagina's met een bepaalde structuur.

Het is heel duidelijk dat deze structuur staat al klaar schijfcache. Door het als cache te gebruiken, wordt ook het probleem van de samenhang opgelost tussen een bestand dat toegankelijk is via lezen/schrijven en hetzelfde bestand dat in het geheugen is toegewezen.

De in de cache opgeslagen I/O-paden komen dus binnen schijf bestand(FsRtlCopyRead op Windows en het soortgelijke generic_file_read() op Linux) worden geïmplementeerd als het kopiëren van gegevens naar fysieke pagina's die aan een bestand zijn toegewezen.

Deze cache-organisatie is uniek in Windows; dit besturingssysteem heeft helemaal geen klassieke schijfblokcache. Metagegevens bestandssystemen in de cache opgeslagen door dummybestanden (IoCreateStreamFileObject) te maken en er een paginacache voor te maken.

Beveiligingsoverwegingen[ | ]

Aanvankelijk had de x86-architectuur geen vlag ‘pagina niet beschikbaar voor uitvoering’ ().

Ondersteuning voor deze vlag verscheen in de x86-architectuur als onderdeel van de PAE-modus (Physical Address Extension) in de Pentium 4-generatie, onder grote druk van beveiligingsspecialisten (zie NTBugTraq-archieven). Door deze vlag op de stack- en heap-pagina's in te stellen, kunt u hardwarebescherming implementeren tegen het uitvoeren van gegevens, waardoor het voor veel soorten malware onmogelijk wordt om te werken, inclusief bijvoorbeeld de kwaadwillige exploitatie van veel kwetsbaarheden in Internet Explorer(Inbreuk van december 2008, zie MS kennis basis, kan niet worden gebruikt als DEP is ingeschakeld).

PAE-ondersteuning in Windows, die het mogelijk maakt om bescherming tegen gegevensuitvoering in te schakelen, verscheen in Windows 2000; het is standaard ingeschakeld in serverversies van Windows en uitgeschakeld in clientversies.

Geheugenondersteuning van meer dan 4 GB op Windows[ | ]

PCI-apparaten, inclusief videokaartgeheugen, ondersteunen doorgaans alleen 32-bits adressen. Daarom moeten ze fysieke adressen onder de 4 GB-markering krijgen. Dit "diafragma" reduceert de hoeveelheid zichtbaar fysiek geheugen onder de 4 GB-markering tot ongeveer 3,2 GB. De rest van het fysieke geheugen wordt opnieuw toegewezen door de controller boven de 4 GB-markering.

Voor elke geheugentoegang boven de grens van 4 GB (d.w.z. meer dan ongeveer 3,2 GB) is controllerondersteuning vereist (d.w.z. noordelijke brug chipset) van deze configuratie. Moderne chipsets (bijvoorbeeld Intel G33) hebben dergelijke ondersteuning.

Ook vereist BIOS-instellingen gerechtigd geheugen opnieuw toewijzen, waarbij de regio wordt toegewezen aan .

De x86-processor buiten de PAE-modus gebruikt 32-bit PTE en fysieke adressen, dat wil zeggen dat hij geen toegang heeft tot iets boven de 4 GB-markering (zie ook PSE-36 voor een van de bypass-opties deze beperking). Als het besturingssysteem dus meer dan ongeveer 3,2 GB geheugen wil gebruiken, moet het PAE ondersteunen. Voor Windows is dit de opstartoptie, voor Linux is dit de kernelbuildoptie.

Bovendien heeft Microsoft om politieke en marketingredenen de ondersteuning voor fysieke adressen groter dan 4 GB gedwongen uitgeschakeld in de volgende besturingssystemen:

Ondersteuning voor fysieke adressen groter dan 4 GB is beschikbaar in de volgende versies:

- alle 64-bits versies,

- 32-bits Windows Vista SP1 (ondersteuning is standaard ingeschakeld, maar voor het inschakelen ervan zijn vaak opdrachten op de opdrachtregel vereist),

- 32-bits Windows-server 2003, anders dan webeditie,

- Windows Server 2008 32-bits.

Om geheugen van meer dan 3,2 GB in Windows te gebruiken, hebt u dus het volgende nodig:

- chipset-ondersteuning,

- correcte BIOS-instellingen,

- juiste versie van Windows

- juiste opstartoptie (met PAE-ondersteuning),

- ondersteuning voor 36-bits adresruimte door apparaatstuurprogramma's.

Maar zelfs in een “uitgeklede” versie van Windows die geen adressen groter dan 4 GB ondersteunt, is het zinvol om altijd PAE te gebruiken, omdat (zie hierboven) bescherming voor gegevensuitvoering (DEP) ook PAE vereist. Wanneer PAE is ingeschakeld, werkt een klein deel van de software mogelijk niet meer, bijvoorbeeld een emulator Windows mobiel. Volgens de ambtenaar Microsoft-versies is de introductie van een beperking van de adresruimte van 4 GB te wijten aan de ontbrekende of slechte ondersteuning voor de 36-bits adresruimte van sommige apparaatstuurprogramma's. Houd er rekening mee dat dit vanwege hardwarebeperkingen of ongeschikte stuurprogramma's onmogelijk is schakel PAE in op versies die fysieke adressen van meer dan 4 GB ondersteunen. De mogelijkheid om PAE in of uit te schakelen is niet afhankelijk van stuurprogramma's, maar als het stuurprogramma van sommige oude PCI-apparatuur fysieke adressen die niet in 32 bits passen niet correct ondersteunt, dan dit apparaat werkt niet correct en kan ervoor zorgen dat de hele computer vastloopt.

Paginageheugenorganisatie wordt alleen gebruikt in beveiligde modus, als in het besturingsregister CR0 de PG-bit = 1.

Het belangrijkste gebruik van pagina-adresvertaling is de implementatie van virtueel geheugen, waardoor de programmeur meer geheugenruimte kan gebruiken dan fysiek hoofdgeheugen.

Beginsel virtueel geheugen gaat ervan uit dat de gebruiker bij het voorbereiden van zijn programma niet te maken heeft met een fysiek RAM-geheugen, dat feitelijk als onderdeel van de computer werkt en een bepaalde vaste capaciteit heeft, maar met virtueel (schijnbaar) single-level geheugen, waarvan de capaciteit gelijk is aan de gehele adresruimte, bepaald door de grootte van de adresbuscomputer (Lsha):

Voor 32-bits microprocessor:

De programmeur beschikt over een adresruimte die alleen wordt beperkt door de breedte van de adresbus, ongeacht de werkelijke capaciteit van het RAM-geheugen van de computer en de hoeveelheid geheugen die wordt gebruikt door andere programma's die parallel worden verwerkt in een computer met meerdere programma's.

Virtueel geheugen, dat de programmeur de mogelijkheid biedt om toegang te krijgen tot een zeer groot volume aaneengesloten adresruimte dat tot zijn exclusieve beschikking staat, heeft de gebruikelijke eigenschappen: byte-byte-adressering, toegangstijd vergelijkbaar met de toegangstijd tot RAM.

In alle fasen van de programmavoorbereiding, inclusief het laden in het geheugen, wordt het programma weergegeven in virtuele adressen, en alleen wanneer een machineopdracht wordt uitgevoerd, worden virtuele adressen omgezet in fysieke adressen. Voor elk programma dat in de multiprogrammamodus wordt uitgevoerd, wordt zijn eigen virtuele geheugen aangemaakt. Elk programma gebruikt dezelfde virtuele adressen van nul tot de grootste in een bepaalde architectuur.

Om virtuele adressen naar fysieke adressen om te zetten, worden het fysieke en virtuele geheugen verdeeld in zogenaamde blokken met een vaste lengte Pagina's. De volumes van virtuele en fysieke pagina's zijn hetzelfde. Virtuele en fysieke geheugenpagina's zijn genummerd. Pagina's die ontbreken in het fysieke geheugen, worden meestal opgeslagen in het externe geheugen. Door de vaste grootte van alle pagina's kunt u elke gewenste virtuele pagina in elke fysieke pagina laden.

Zoals hierboven opgemerkt, is bij wisselbaar geheugen het virtuele (logische) adres het virtuele paginanummer en de offset binnen die pagina. Het fysieke adres is op zijn beurt het nummer van de fysieke pagina en de offset daarin.

De regels voor het vertalen van virtuele paginanummers naar fysieke paginanummers worden meestal gespecificeerd in de vorm van een pagineringstabel. Dergelijke tabellen worden gevormd door het geheugenbeheersysteem en worden elke keer gewijzigd wanneer geheugen opnieuw wordt toegewezen. Het besturingssysteem controleert voortdurend de status van de virtuele pagina's van een programma en bepaalt of het zich in het RAM bevindt, en zo ja, op welke specifieke locatie. Applicatieprogramma's worden niet beïnvloed door het pagingproces en kunnen de volledige adresruimte gebruiken. De processor genereert automatisch een speciaal geval van niet-aanwezigheid wanneer een programma toegang krijgt tot een pagina die zich niet in het fysieke geheugen bevindt. Bij het afhandelen van dit speciale geval laadt het besturingssysteem de gevraagde pagina uit het externe geheugen, waarbij optioneel een andere pagina naar schijf wordt verzonden (swapproces).

De vertaling van virtuele adressen naar fysieke adressen wordt geïllustreerd in Fig. 3.12.

Rijst. 3.12. Het principe van het omzetten van een virtueel paginaadres naar een fysiek paginaadres

Laten we eens kijken naar een voorbeeld van het converteren van een virtueel paginaadres naar een fysiek paginaadres. Laat de computer een pagingadresruimte van V pagina = 1I gebruiken en RAM V RAM = 3 pagina's hebben. Laat vier programma's tegelijkertijd worden uitgevoerd op een computer met het volgende aantal pagina's: VA = 2, VB = 1, VC = 3, V D = 2. Het schakelen tussen programma's gebeurt via kwantumtijd t k = 1. De uitvoeringstijd van elke pagina van elk programma is t = 2t k. Wij zijn van mening dat programmapagina's indien nodig in het RAM worden geladen en, indien mogelijk, in vrije RAM-gebieden. Als al het geheugen bezet is, vervangt een nieuwe pagina de pagina die het langst niet is geopend.

Onder dergelijke omstandigheden zullen de RAM-laadtabel en de paginaconversietabellen voor elk programma de vorm hebben die in de tabel wordt weergegeven. 3.2.

In de RAM-distributietabel worden de aantallen pagina's die actief zijn in een bepaalde cyclus gemarkeerd. In de paginaconversietabellen geven streepjes situaties aan waarin een bepaalde virtuele pagina zich niet in het RAM bevindt.

| Tabel 3.2. Een voorbeeld van paginageheugentoewijzing in een computer met meerdere programma's | |||||||||||||||||

| Bladzijde | Dus jij | ||||||||||||||||

| Dynamische geheugentoewijzing | |||||||||||||||||

| RAM-geheugen 0 | JSC | JSC | JSC | DOEN | DOEN | DOEN | CO | CO | CO | C1 | C1 | C1 | C1 | C1 | C1 | C1 | |

| B0 | B0 | B0 | A0 | A0 | A0 | D0 | D0 | D0 | D1 | D1 | D1 | D1 | D1 | D1 | |||

| C0 | C0 | C0 | B0 | B0 | B0 | A1 | A1 | A1 | A1 | A1 | A1 | C2 | C2 | ||||

| Pagingtabel voor programma A | |||||||||||||||||

| Een 0 | - | - | - | - | - | - | - | - | - | - | - | ||||||

| - | - | - | - | - | - | - | - | - | - | ||||||||

| Pagingtabel voor programma B | |||||||||||||||||

| B0 | - | - | - | - | - | - | - | - | - | - | |||||||

| Pagingtabel voor programma C | |||||||||||||||||

| Vanaf 0 | - | - | - | - | - | - | - | - | - | - | |||||||

| - | - | - | - | - | - | - | - | - | |||||||||

| - | - | - | - | - | - | - | - | - | - | - | - | - | - | ||||

| Pagingtabel voor programma D | |||||||||||||||||

| D0 | - | - | - | - | - | - | - | - | - | - | |||||||

| - | - | - | - | - | - | - | - | - | - |

Als elke pagina een capaciteit heeft van 1000 adresseerbare cellen, zal bijvoorbeeld in klokcyclus 9 toegang tot virtueel adres 1100 van programma A (virtuele pagina 1, pagina-offset is 100) resulteren in toegang tot fysiek adres 2100 (fysieke pagina 2, fysieke pagina heeft dezelfde offset als de virtuele pagina, dat wil zeggen 100).

Laten we nu de toepassing bekijken van deze algemene principes van paginaadresvertaling in een microprocessor met IA-32-architectuur met een paginagrootte van 4 KB.

De pagingbasis is 32-bit lineair adres, verkregen in de fase van segmenttransformatie logisch adres. Er wordt opgeroepen wanneer de PG-bit in het besturingsregister CRO op 1 wordt ingesteld.

In dit geval de hoogste 20 bits lineair adres vertegenwoordigt feitelijk het virtuele paginanummer. Voor een directe conversie in één stap van dit nummer naar een fysiek paginanummer is echter een tabel nodig van 220 elementen van elk 4 bytes lang (20-bits paginanummer plus enige aanvullende informatie), d.w.z. 4 MB. In een multiprogrammeeromgeving kan een dergelijke tabel voor elke taak nodig zijn. Deze tabel moet permanent in het RAM worden opgeslagen om de tijd die nodig is om een fysiek adres te genereren niet aanzienlijk te verlengen. Voor deze doeleinden zal het noodzakelijk zijn om voortdurend een aanzienlijk deel van de RAM-capaciteit te reserveren, wat praktisch onmogelijk was in het stadium van de opkomst van de eerste MP-gebaseerde computers met de IA-32-architectuur.

In plaats daarvan gebruikt de microprocessor adresoproep in twee fasen. De hoofdpagina, genaamd paginatabelmap(KTS), bevat 1024 32-bits paginatabel directory-element(ECTS - PDE-paginamapinvoer). Elk van hen richt zich tot een ondergeschikte pagina tabel(TS), dat wil zeggen dat er in totaal maximaal 1024 slavepaginatabellen zijn toegestaan. Elke paginatabel bevat 1024 32-bits paginatabelelement(ETS - PTE-paginatabelinvoer), die elk een fysieke pagina adresseren. Het totale aantal adresseerbare fysieke pagina's is dus 2 20, dat wil zeggen de gehele virtuele adresruimte (4 KB * 220 elementen = 2 32 bytes). Elke tabel beslaat 1024 4 = 4 KB, dat wil zeggen precies 1 pagina. De totale omvang van de voor paging gebruikte tabellen is niet afgenomen, maar zelfs licht toegenomen door het gebruik van de paginatabelcatalogus. Ten eerste kan deze omvang echter bijna altijd in een systeem aanzienlijk worden verkleind vanwege het feit dat sommige lineaire adressen zal nooit worden gevormd (en deze informatie wordt gegeven descriptortabellen segmenten) en hoeft u er geen paginatabel voor te maken. En ten tweede alleen de paginatabel directory en paginatabel momenteel actief programma. Rest pagina tabellen kan tijdelijk worden opgeslagen in een extern geheugen.

Rijst. 3.13. Lineaire naar fysieke adrespaginaconversie

De conversie van een lineair adres naar een fysiek adres heeft dus de vorm getoond in Fig. 3.13.

Bovenste 20 cijfers lineair adres worden opgesplitst in twee 10-bits velden: veld paginatabel catalogusartikelnummers en veld paginatabelelementnummers. Sinds paginatabelmap, en elk pagina tabel bezetten precies 1 pagina en zijn uitgelijnd met een paginagrens, dan zijn de onderste 12 bits van hun basisadres nul, en is een veld van 20 bits voldoende om hun fysieke adres te bepalen.

Voor paginatabelmap het 20-bits adres bevindt zich in besturingsregister CR3. De CTS bevindt zich permanent in het geheugen en neemt niet deel aan het wisselen.

De bovenste 20 bits van het fysieke adres pagina tabellen worden uit het ETS gehaald. De structuren van het CTS-element en het TS-element zijn vergelijkbaar (Fig. 3.14).

Rijst. 3.14. Structuur van paginatabelcataloguselementen en paginatabellen

De meest significante 20 bits van het element geven het basisadres pagina tabellen(in ECTS) of fysieke pagina (in ETS). De P-, A-, R/W- en U/S-bits hebben bepaalde overeenkomsten met die van de segmentdescriptor; andere bits hebben specifieke doeleinden.

Aanwezigheidsstukje P geeft aan of het adres van een paginaframe (paginatabel of geheugenpagina) is toegewezen aan een pagina in het fysieke geheugen. Wanneer P = 1, is de pagina aanwezig in RAM. Wanneer P = 0, is er geen pagina in het geheugen, en toegang tot deze pagina veroorzaakt een paginafoutonderbreking.

Toegangsbit A wordt door de microprocessor ingesteld op toestand A = 1 bij toegang tot dit paginaframe om informatie te schrijven of te lezen.

Wijziging stukje D (Dirty - “dirty”) wordt door de processor gelijkgesteld aan 1 in het ETS-element bij het schrijven naar deze pagina. Voor paginatabeldirectory-items is de waarde van de D-bit ongedefinieerd. Bij het laden van een pagina in het geheugen reset het besturingssysteem bit D. Als, wanneer het nodig is om een pagina in het externe geheugen te laden, blijkt dat D = 0 ervoor is, betekent dit dat er geen schrijftoegang tot de pagina in het geheugen was. geheugen; er staat een exacte kopie ervan in het externe geheugen, en het is niet nodig om de pagina daadwerkelijk van het geheugen naar de schijf over te brengen. Dit bespaart tijd bij het wisselen.

De lees-schrijfbit R/W en de U/S-bit (gebruiker/supervisor) bepalen de toegangsrechten tot de paginatabel of pagina voor programma's met verschillende rechtenniveaus. Er zijn slechts 2 rechtenniveaus voor pagina's: supervisorniveau (U/S = 0), overeenkomend met de waarde DPL van segment 0, 1, 2 en gebruikersniveau (U/S = 1) overeenkomend met DPL = 3. Als er een verzoek wordt gedaan naar de pagina met privilegeniveau 3 (gebruikersprogramma's), dan met een waarde van U/S = 0 de toegang tot de bijbehorende tabel of pagina wordt geweigerd. Als U/S = 1, dan is wanneer R/W = 0 alleen het lezen van de tabel of pagina toegestaan, en wanneer R/W = 1 is zowel lezen als schrijven toegestaan.

Voor verzoeken met hoge rechten (system programma niveaus 0, 1, 2) schrijven en lezen van tabellen en pagina's is toegestaan voor alle waarden van U/S, R/W (Tabel 3.3).

De PWT- en PCD-bits worden gebruikt om de werking van het cachegeheugen tijdens pagina-adressering te regelen. PCD-bit - paginacaching uitschakelen. Wanneer PCD = 1, is caching uitgeschakeld. De PWT-bit is de pagina-terugschrijfbit. Definieert de methode voor het bijwerken van de externe cache (L2-cache). Wanneer PWT = 1, wordt de update uitgevoerd met behulp van de write-through-methode (net als voor de interne cache), wanneer PWT = 0, met behulp van de write-back-methode.

Bits 9...11 in ECTS en ETS zijn gereserveerd voor het besturingssysteem. De processor gebruikt of wijzigt deze bits nooit. OS-ontwikkelaars kunnen deze bits gebruiken om informatie over paginaveroudering op te slaan, om te bepalen welke pagina's uit het externe geheugen moeten worden vervangen, en voor andere doeleinden.

Senioren 10 cijfers lineair adres bepalen samen met de inhoud van het besturingsregister CR3 het vereiste paginatabel directory-element. De volgende 10 bits van het lineaire adres bevatten het elementnummer in de geselecteerde paginatabel.

Omdat zowel ECTS als ETS 4 bytes lang zijn, moet het getal met 4 worden vermenigvuldigd om de offset van het begin van een element ten opzichte van het begin van de overeenkomstige tabel te verkrijgen.

Laatste 12 cijfers lineair adres een offset op de pagina bevatten. De som van de pagina-offset en het paginabasisadres dat uit de ETS wordt gehaald, geeft dus het fysieke adres van de gezochte byte.

In oproepsystemen zijn de hoofd- en extern geheugen(voornamelijk schijfruimte) zijn verdeeld in blokken of pagina's met een vaste lengte. Elke gebruiker beschikt over een bepaald deel van de adresruimte, dat het hoofdgeheugen van de computer kan overschrijden en dat alleen wordt beperkt door de adresseringsmogelijkheden die inherent zijn aan het instructiesysteem. Dit deel van de adresruimte wordt virtueel gebruikersgeheugen genoemd. Elk woord in het virtuele geheugen van de gebruiker wordt bepaald door een virtueel adres, dat uit twee delen bestaat: de bits van hoge orde van het adres worden beschouwd als het paginanummer, en de bits van lage orde worden beschouwd als het nummer van het woord (of byte) binnen de pagina.

De verschillende geheugenniveaus worden beheerd door kernelprogramma's van het besturingssysteem die de paginatoewijzing controleren en de uitwisseling tussen deze niveaus optimaliseren. Met geheugenpaging hoeven aaneengesloten virtuele pagina's zich niet op aaneengesloten pagina's van het fysieke hoofdgeheugen te bevinden. Om correspondentie aan te geven tussen virtuele pagina's en hoofdgeheugenpagina's moet het besturingssysteem voor elk programma een paginatabel vormen en deze in het hoofdgeheugen van de machine plaatsen. In dit geval wordt elke pagina van het programma, ongeacht of deze zich in het hoofdgeheugen bevindt of niet, geassocieerd met een bepaald element van de paginatabel. Elk paginatabelelement bevat een fysiek paginanummer in het hoofdgeheugen en een speciale indicator. Een enkele status van deze indicator geeft de aanwezigheid van deze pagina in het hoofdgeheugen aan. De nulstatus van de indicator betekent dat er geen pagina in het RAM is.

Om de efficiëntie van dit type circuits te vergroten, gebruiken processors een speciaal, volledig associatief cachegeheugen, ook wel een translation-lookaside buffer (TLB) genoemd. Hoewel de aanwezigheid van een TLB het principe van het pagingontwerp niet verandert, is het vanuit het oogpunt van geheugenbescherming noodzakelijk om de mogelijkheid te bieden om deze te wissen wanneer van het ene programma naar het andere wordt overgeschakeld.

Het doorzoeken van de paginatabellen in het hoofdgeheugen en het laden van de TLB kan ook worden gedaan programmatisch of speciale hardware. In het laatste geval om de mogelijkheid tot verhaal te voorkomen gebruikersprogramma Paginatabellen waaraan deze niet is gekoppeld, zijn onderworpen aan speciale maatregelen. Voor dit doel biedt de processor een extra beschermingsregister dat een paginatabeldescriptor of een base-grenspaar bevat. De basis bepaalt het adres van het begin van de paginatabel in het hoofdgeheugen, en de grens bepaalt de lengte van de paginatabel van het overeenkomstige programma. Het laden van dit beveiligingsregister is alleen toegestaan in de bevoorrechte modus. Voor elk programma slaat het besturingssysteem een paginatabelhandle op en plaatst deze in het beveiligingsregister van de processor voordat het bijbehorende programma wordt uitgevoerd.

Laten we enkele inherente kenmerken opmerken eenvoudige schakelingen met paginageheugenorganisatie. De belangrijkste hiervan is dat alle programma's die rechtstreeks met elkaar moeten communiceren zonder tussenkomst van het besturingssysteem een gemeenschappelijke virtuele adresruimte moeten gebruiken. Dit geldt ook voor besturingssysteem, die over het algemeen zou moeten werken in de dynamische geheugentoewijzingsmodus. Daarom wordt in sommige systemen de virtuele adresruimte van de gebruiker ingekort door de grootte van de algemene procedures waartoe gebruikersprogramma's toegang willen hebben. Algemene procedures Aan alle gebruikers moet een bepaalde hoeveelheid virtuele adresruimte worden toegewezen, zodat ze een vaste plaats hebben in de paginatabellen van alle gebruikers. In dit geval moet worden gezorgd voor geheimhouding en wederzijdse isolatie van de uitvoerende programma's om de integriteit te garanderen verschillende modi toegang tot pagina's, die worden geïmplementeerd met behulp van speciale toegangsindicatoren in paginatabelelementen.

Het gevolg van dit gebruik is een aanzienlijke toename van de paginatabellen van elke gebruiker. Eén oplossing voor het probleem van het reduceren van de lengte van tabellen is gebaseerd op de introductie van een indeling van tabellen op meerdere niveaus. Een speciaal geval van de organisatie van tabellen op meerdere niveaus is segmentatie met paginageheugenorganisatie. De noodzaak om de adresruimte van de gebruiker te vergroten wordt verklaard door de wens om de noodzaak te vermijden om delen van programma's en gegevens binnen de adresruimte te verplaatsen, wat meestal leidt tot hernoemingsproblemen en ernstige problemen bij het partitioneren algemene informatie tussen vele taken.

Einde van het werk -

Dit onderwerp behoort tot de sectie:

Principes van computerbediening. Een leerboek voor de cursussen “Programmeertechnologie” en “Besturingssystemen”

De handleiding schetst Basisprincipes organisatie en werking van een computer, de samenstelling van een minimale computer met busorganisatie, doel en.. naam bibliograaf..

Als je nodig hebt aanvullend materiaal over dit onderwerp, of als u niet hebt gevonden wat u zocht, raden wij u aan de zoekopdracht in onze database met werken te gebruiken:

Wat gaan wij met het ontvangen materiaal doen:

Als dit materiaal nuttig voor u was, kunt u het op uw pagina op sociale netwerken opslaan:

| Tweeten |

Alle onderwerpen in deze sectie:

Principes van Von Neumann

Meerderheid moderne computers zijn gebouwd op basis van principes geformuleerd door de Amerikaanse wetenschapper, een van de ‘vaders’ van de cybernetica, J. von Neumann. Deze principes werden voor het eerst gepubliceerd door von Neumann in 19

Samenstelling en werking van een minimale computer met een busorganisatie

De busorganisatie is eenvoudigste vorm computer organisaties. Zo'n computer bevat de volgende functionele blokken (zie figuur 1). Besturingsapparaat (CU) -

Computeropdrachten

IN deze sectie In de handleiding wordt kort ingegaan op de reeks commando's die op typische computers worden gebruikt, en op de acties die door deze commando's worden geïmplementeerd.

De eerste van de commando's (vergelijking), zoals hierboven vermeld, trekt de waarde van operand B af van operand A. Als A>B, dan zal het resultaat positief zijn en dienovereenkomstig de tekenvlag in het vlagregister

Systeeminterfaces met geïsoleerde en gemeenschappelijke bussystemen

In de voorgaande secties, bij het beschrijven van het algemene bedieningsalgoritme centrale verwerker we hebben bewust de vraag weggelaten hoe de processor externe apparaatpoorten ‘onderscheidt’ van cellen

Methoden voor gegevensuitwisseling in machines met een busorganisatie. Onderbreekmechanisme

Nadat we het algoritme voor de werking van de processor en de methoden voor het organiseren van het bussysteem in een computer hebben onderzocht, zullen we proberen erachter te komen welke kenmerken de noodzaak om interactie te garanderen introduceert in de werking en organisatie van een computer.

Softwaregestuurde gegevensuitwisseling

Sinds de snelheid van werken randapparatuur meestal onder de processorsnelheid, om een uitwisselingsoperatie uit te voeren, moet de processor ervoor zorgen dat het apparaat gereed is om de operatie uit te voeren

Onderbreek de uitwisseling

Om te begrijpen wat een interrupt is, kijken we naar het volgende voorbeeld. Een man zit in een stoel en leest een boek. Op dit moment wordt er iets gekookt op het fornuis, en bovendien

Directe geheugentoegang buiten de processor

Communicatie met langzaam bewegend randapparatuur Bij een karakter-voor-karakter-printer is het bijvoorbeeld georganiseerd rond interrupts die de overdracht van elk woord of byte initiëren. Als de subroutine

En meer over onderbrekingen

Het hierboven beschreven interruptmechanisme, of hardware-interrupts, is effectieve manier het organiseren van de interactie van de processor met langzame externe apparaten en begon

Adresseringsmodi

Tijdens de uitvoering van het programma hebben veel opdrachten toegang tot het geheugen nodig om gegevens op te halen en tussen- en definitieve berekeningsresultaten te schrijven. Voor elke dergelijke behandeling, zoals reeds vermeld in

Hiërarchische organisatie van het geheugen

Geheugen in moderne computers wordt gebouwd volgens hiërarchisch principe. Een van de verschijnselen die kenmerkend zijn voor von Neumann-computers is het lokaliteitsprincipe. Dit betekent dat binnen een beperkte periode

Cachegeheugen

Zoals hierboven vermeld, is het doel van cachegeheugen het tijdelijk opslaan van gegevens en instructies die vaak door de processor worden gebruikt. De structurele basiseenheid van het cachegeheugen is de zogenaamde cacheregel (ca

Segmentale organisatie van virtueel geheugen

Een andere benadering van geheugenorganisatie berust op het feit dat programma's doorgaans in afzonderlijke segmentgebieden zijn verdeeld. Elk segment vertegenwoordigt een afzonderlijke logische informatie-eenheid,

Omleidingsproces voor virtueel geheugen

We zullen het omleidingsproces beschrijven aan de hand van het voorbeeld van de 80386-microprocessor van Intel. Het omleidingsproces wordt getoond in Fig. 19 en 20. Vóór uitvoering worden opstartmodellen in de operationele versie geplaatst

Gegevensformaten

De belangrijkste soorten gegevens die men tegenkomt bij het verwerken van informatie in een computer zijn getallen die worden weergegeven in binair systeem cijfers en alfanumerieke tekens. Sommige computers ook

Computerinformatiemodel

Verwerking van getallen, symbolische informatie, logische verwerking signaalverwerking zijn allemaal speciale gevallen algemeen concept boven de titel "informatieverwerking". Een computer kenmerkt zich door: informatie

De eenvoudigste transportband, transportbandprestaties

Er is een vrij eenvoudige bekende regel: om een bepaald werk sneller te voltooien, moet je het over meerdere artiesten verdelen en ze dwingen tegelijkertijd te handelen. Eenmaal

Structurele conflicten

Structurele conflicten ontstaan als verschillende delen van de pijpleiding toegang krijgen tot één enkele, niet-dubbele hulpbron. Gelijke situatie treedt bijvoorbeeld op als de processor een single heeft

Gegevensconflicten

Dataconflicten ontstaan wanneer verschillende opeenvolgend uitgevoerde opdrachten logisch van elkaar afhankelijk blijken te zijn. Als de volgorde van gegevenstoegang tijdens pijplijnverwerking zeker is

Het verminderen van verliezen bij het uitvoeren van transitiecommando's en het minimaliseren van controleconflicten

Controleconflicten kunnen zelfs grotere prestatieverliezen in de pipeline veroorzaken dan dataconflicten. Wanneer een voorwaardelijke aftakkingsinstructie wordt uitgevoerd, kan deze wel of niet veranderen

Computer met kanaalorganisatie

Dit type computerorganisatie is gebaseerd op de veelheid aan communicatiekanalen tussen apparaten en de functionele specialisatie van knooppunten. Een vereenvoudigd diagram van de organisatie van een computer met kanalen wordt getoond in Fig.