I lang tid har utviklere skapt Forskjellige typer hukommelse. De hadde forskjellige egenskaper, de brukte forskjellige tekniske løsninger. Den viktigste drivkraften bak utviklingen av minne var utviklingen av datamaskiner og sentrale behandlingsenheter. Det var et konstant behov for å øke hastigheten og mengden RAM.

Sideminne

Sidemodus DRAM (PM DRAM) var en av de første typene datamaskin-RAM produsert. Minne av denne typen ble produsert på begynnelsen av 1990-tallet, men med økningen i prosessorytelse og ressursintensitet til applikasjoner, var det nødvendig å øke ikke bare mengden minne, men også hastigheten på driften.

Rask sideminne

Hurtigsideminne (eng. hurtigsidemodus DRAM, FPM DRAM) dukket opp i 1995. Minnet gjennomgikk ingen fundamentalt nye endringer, og økningen i driftshastighet ble oppnådd ved å øke belastningen på minnemaskinvaren. Denne typen minne ble hovedsakelig brukt til datamaskiner med Intel 80486-prosessorer eller lignende prosessorer fra andre selskaper. Minnet kunne operere ved frekvenser på 25 og 33 MHz med full tilgangstid på 70 og 60 ns og driftssyklustider på henholdsvis 40 og 35 ns.

EDO DRAM -- minne med forbedret utgang

Med fremveksten av prosessorer Intel Pentium FPM DRAM var fullstendig ineffektiv. Derfor var neste trinn minne med forbedret utgang (utvidet data ut DRAM, EDO DRAM). Dette minnet dukket opp på markedet i 1996 og begynte å bli aktivt brukt på datamaskiner med Intel Pentium-prosessorer og høyere. Ytelsen var 10-15 % høyere sammenlignet med minne av typen FPM DRAM. Driftsfrekvensen var henholdsvis 40 og 50 MHz, full tilgangstid var 60 og 50 ns, og driftssyklustiden var 25 og 20 ns. Dette minnet inneholder en datalås for utdataene, som gir noe pipelining for forbedret leseytelse.

SDRAM -- synkron DRAM

På grunn av utgivelsen av nye prosessorer og en gradvis økning i frekvens systembuss, begynte stabiliteten til EDO DRAM-minnet å synke merkbart. Det ble erstattet av synkront minne (eng. synchronous DRAM, SDRAM). Nye funksjoner ved denne typen minne var bruken klokkegeneratorå synkronisere alle signaler og bruke rørledningsinformasjonsbehandling. Minnet fungerte også pålitelig ved høyere systembussfrekvenser (100 MHz og høyere).

Hvis for FPM- og EDO-minne lesetiden til den første cellen i kjeden (tilgangstid) er indikert, så for SDRAM er lesetiden for påfølgende celler indikert. En kjede er flere påfølgende celler. Det tar ganske mye tid å lese den første cellen (60-70 ns), uavhengig av type minne, men tiden for å lese de påfølgende avhenger i stor grad av typen. Driftsfrekvensene til denne typen minne kan være 66, 100 eller 133 MHz, full tilgangstid var 40 og 30 ns, og driftssyklustiden var 10 og 7,5 ns.

Virtual Channel Memory (VCM)-teknologi ble brukt med denne typen minne. VCM bruker arkitektur virtuell kanal, som muliggjør mer fleksibel og effektiv dataoverføring ved bruk av registerkanaler på brikken. Denne arkitekturen er integrert i SDRAM. VCM, i tillegg høy hastighet dataoverføring, var kompatibel med eksisterende SDRAM, noe som gjorde det mulig å oppgradere systemet uten vesentlige kostnader og modifikasjoner. Denne løsningen har funnet støtte fra enkelte brikkesettprodusenter.

Forbedret SDRAM (ESDRAM)

For å overvinne noen av signallatensproblemene som er iboende i standard DRAM-minne, ble det besluttet å legge inn en liten mengde SRAM på brikken, det vil si å lage en cache på brikken.

ESDRAM er i hovedsak SDRAM med en liten mengde SRAM. Med lav latens og burst-drift oppnås frekvenser opp til 200 MHz. Som med eksternt hurtigbufferminne, er SRAM-hurtigbufferen designet for å lagre og hente de mest brukte dataene. Derav reduksjonen i datatilgangstiden for treg DRAM.

En slik løsning var ESDRAM fra Ramtron International Corporation.

Batch EDO RAM

EDO RAM (burst extended data output DRAM, BEDO DRAM) har blitt et billig alternativ til SDRAM. Basert på EDO DRAM, var nøkkelfunksjonen blokk-for-blokk-teknologi (en blokk med data ble lest i en klokkesyklus), noe som gjorde det raskere enn SDRAM. Men manglende evne til å operere med en systembussfrekvens på mer enn 66 MHz tillot ikke denne typen minne å bli populær.

En spesiell type RAM - Video RAM (VRAM) - ble utviklet basert på SDRAM-minne for bruk i skjermkort. Det muliggjorde en kontinuerlig flyt av data under bildeoppdateringsprosessen, noe som var nødvendig for å realisere bilder av høy kvalitet. Basert på minnetype VRAM, en minnespesifikasjon som Windows RAM(WRAM), noen ganger feilaktig assosiert med operativsystemer Windows-familien. Ytelsen er 25 % høyere enn den originale SDRAM, takket være noen tekniske endringer.

Sammenlignet med vanlig minne skriv SDRAM, inn SDRAM-minne med dobbel datahastighet SDRAM, DDR SDRAM eller SDRAM II ble gjennomstrømningen doblet. Opprinnelig ble denne typen minne brukt i skjermkort, men senere dukket støtte for DDR SDRAM opp på brikkesettsiden.

Alle tidligere DRAM-er hadde separate adresse-, data- og kontrolllinjer, noe som påla begrensninger på enhetenes hastighet. For å overvinne denne begrensningen har noen teknologiløsninger implementert alle signaler på en enkelt buss. To av disse løsningene er DRDRAM- og SLDRAM-teknologier. De har fått mest popularitet og fortjener oppmerksomhet. SLDRAM-standarden er åpen og, som tidligere teknologi, bruker SLDRAM begge klokkekantene. Når det gjelder grensesnittet, bruker SLDRAM en protokoll kalt SynchLink Interface og har som mål å operere på 400 MHz.

DDR SDRAM-minne opererer ved frekvenser på 100, 133, 166 og 200 MHz, full tilgangstid er 30 og 22,5 ns, og driftssyklustid er 5, 3,75, 3 og 2,5 ns.

Siden klokkefrekvensen varierer fra 100 til 200 MHz, og data overføres med 2 bits per klokkepuls, både på kanten og ved fall av klokkepulsen, ligger den effektive dataoverføringsfrekvensen i området fra 200 til 400 MHz. Slike minnemoduler er betegnet DDR200, DDR266, DDR333, DDR400.

Direct RDRAM eller Direct Rambus DRAM

RDRAM-minnetypen er utviklet av Rambus. Den høye ytelsen til dette minnet oppnås av en rekke funksjoner som ikke finnes i andre typer minne. De opprinnelige svært høye kostnadene for RDRAM-minne førte produsentene til kraftige datamaskiner de foretrakk mindre produktivt, men billigere DDR SDRAM-minne. Minnedriftsfrekvenser er 400, 600 og 800 MHz, full tilgangstid er opptil 30 ns, driftssyklustid er opptil 2,5 ns.

Strukturelt sett ny type DDR2 SDRAM ble utgitt i 2004. Basert på DDR SDRAM-teknologi vil denne typen minne pga tekniske endringer viser høyere ytelse og er beregnet for bruk på moderne datamaskiner. Minnet kan operere med bussklokkehastigheter på 200, 266, 333, 337, 400, 533, 575 og 600 MHz. I dette tilfellet vil den effektive dataoverføringsfrekvensen være henholdsvis 400, 533, 667, 675, 800, 1066, 1150 og 1200 MHz. Noen minnemodulprodusenter, i tillegg til standard frekvenser De produserer også prøver som opererer ved ikke-standard (mellomliggende) frekvenser. De er beregnet for bruk i overklokkede systemer der frekvenshøyde er nødvendig. Full tilgangstid -- 25, 11.25, 9, 7.5 ns eller mindre. Driftssyklustid - fra 5 til 1,67 ns.

Denne typen minne er basert på DDR2 SDRAM-teknologier med dobbelt så høy dataoverføringsfrekvens på minnebussen. Den har lavere strømforbruk sammenlignet med forgjengerne. Båndbreddefrekvensen varierer fra 800 til 2400 MHz (frekvensrekorden er mer enn 3000 MHz), noe som gir større gjennomstrømming sammenlignet med alle forgjengere.

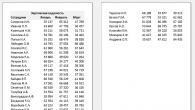

DRAM-minnedesign

Ris. 4. Ulike DRAM-pakker. Fra topp til bunn: DIP, SIPP, SIMM (30-pinners), SIMM (72-pinners), DIMM (168-pinners), DIMM (184-pinners, DDR)

Fig.5.

Ris. 6. DDR2-modul i 204-pinners SO-DIMM-pakke

DRAM-minne er strukturelt implementert både i form av separate mikrokretser i pakker som DIP, SOIC, BGA, og i form av minnemoduler av typen: SIPP, SIMM, DIMM, RIMM.

Opprinnelig ble minnebrikker produsert i DIP-type pakker (for eksempel K565RUxx-serien), deretter begynte de å bli produsert i mer teknologisk avanserte pakker for bruk i moduler.

Mange SIMM-moduler og de aller fleste DIMM-er hadde SPD (Serial Presence Detect) installert – en liten EEPROM-minnebrikke som lagrer modulparametere (kapasitet, type, driftsspenning, antall banker, tilgangstid osv.), som var tilgjengelig i programvare som utstyr som modulen ble installert i (brukes til automatisk konfigurering av parametere), og til brukere og produsenter.

SIPP-moduler

Moduler av typen SIPP (Single In-line Pin Package) er rektangulære kort med kontakter i form av en serie små pinner. Denne typen design brukes praktisk talt ikke lenger, siden den senere ble erstattet av SIMM-type moduler.

SIMM-moduler

SIMM-moduler (Single In-line Memory Module) er lange rektangulære brett med et antall puter langs en av sidene. Modulene festes i tilkoblingskontakten (sokkelen) ved hjelp av låser, ved å installere brettet i en viss vinkel og trykke det til det bringes til vertikal posisjon. Moduler på 4, 8, 16, 32, 64, 128 MB ble produsert.

De vanligste er 30- og 72-pinners SIMM-er.

DIMM-er

Moduler DIMM-type(Dual In-line Memory Module) er lange rektangulære kort med rader med kontaktputer langs begge sider, installert vertikalt i tilkoblingskontakten og festet i begge ender med låser. Minnebrikker på dem kan plasseres på en eller begge sider av brettet.

SDRAM-minnemoduler er mest vanlige i form av 168-pinners DIMM-er, minne DDR type SDRAM er i form av 184-pinners, og moduler som DDR2, DDR3 og FB-DIMM SDRAM er 240-pinners moduler.

SO-DIMM-er

For bærbare og kompakte enheter(Mini-ITX formfaktor hovedkort, bærbare datamaskiner, bærbare datamaskiner, nettbrett osv.), samt skrivere, nettverks- og telekommunikasjonsutstyr osv. Strukturelt reduserte DRAM-moduler (både SDRAM og DDR SDRAM) er mye brukt - SO-DIMM (Small) outline DIMM) - analoger av DIMM-moduler i en kompakt design for å spare plass.

RIMM-moduler

Moduler av RIMM-typen (Rambus In-line Memory Module) er mindre vanlige, de kommer med RDRAM-minne. De er representert av 168- og 184-pinners varianter, og videre hovedkort Slike moduler må bare installeres i par ellers er spesielle pluggmoduler installert i tomme spor (dette er på grunn av designfunksjonene til slike moduler). Det er også 242-pinners PC1066 RDRAM RIMM 4200-moduler, som ikke er kompatible med 184-pinners kontakter, og en mindre versjon av RIMM - SO-RIMM, som brukes i bærbare enheter.

Dynamisk minne inn datamaskin betydelig mer enn statisk, siden det er DRAM som brukes som hovedminnet til VM. Som SRAM består dynamisk minne av en kjerne (en rekke elektroniske enheter) og grensesnittlogikk (bufferregistre, dataleseforsterkere, regenereringskretser, etc.). Selv om antallet typer DRAM allerede har oversteget to dusin, er kjernene deres organisert nesten identisk. Hovedforskjellene er relatert til grensesnittlogikken, og disse forskjellene skyldes også anvendelsesområdet for mikrokretsene - i tillegg til hovedminnet til VM, er dynamiske minne-IC-er inkludert, for eksempel i videoadaptere. Klassifiseringen av dynamiske minnebrikker er vist i fig. 72.

For å evaluere forskjellene mellom typer DRAM, la oss først se på algoritmen for å jobbe med dynamisk minne. For dette vil vi bruke fig. 68.

I motsetning til SRAM, blir adressen til en DRAM-celle overført til brikken i to trinn - først kolonneadressen, og deretter raden, som lar deg redusere antall adressebusspinner med omtrent det halve, redusere størrelsen på saken og plasser den på hovedkortet stor kvantitet mikrokretser Dette fører selvfølgelig til en nedgang i ytelsen, siden det tar dobbelt så lang tid å overføre adressen. For å indikere hvilken del av adressen som sendes på et bestemt tidspunkt, brukes to hjelpesignaler RAS og CAS. Ved tilgang til en minnecelle settes adressebussen til adressen til raden. Etter at prosessene på bussen har stabilisert seg, tilføres RAS-signalet og adressen skrives til det interne registeret til minnebrikken. Adressebussen settes så til kolonneadressen og CAS-signalet sendes. Avhengig av tilstanden til WE-linjen, leses data fra cellen eller skrives til cellen (dataene må plasseres på databussen før skriving). Intervallet mellom innstilling av adressen og utstedelse av RAS (eller CAS)-signal er spesifisert tekniske egenskaper mikrokretser, men vanligvis settes adressen i en klokkesyklus på systembussen, og styresignalet i den neste. For å lese eller skrive én celle med dynamisk RAM, kreves det derfor fem klokkesykluser, der følgende skjer: utstede en radadresse, utstede et RAS-signal, utstede en kolonneadresse, utstede et CAS-signal, utføre en lese-/skriveoperasjon (i statisk minne tar prosedyren bare to til tre tiltak).

Ris. 72. Klassifisering av dynamisk RAM: a) – brikker for hovedminne; b) – mikrokretser for videoadaptere.

Du bør også huske behovet for dataregenerering. Men sammen med den naturlige utladningen av kondensatoren, fører den elektroniske enheten også til tap av ladning over tid ved lesing av data fra DRAM, så etter hver leseoperasjon må dataene gjenopprettes. Dette oppnås ved å skrive de samme dataene på nytt umiddelbart etter lesing. Når du leser informasjon fra en celle, sendes faktisk dataene til hele den valgte raden ut samtidig, men bare de som er i interessekolonnen brukes, og resten blir ignorert. Dermed ødelegger en leseoperasjon fra en enkelt celle hele radens data og må gjenopprettes. Dataregenerering etter lesing utføres automatisk av grensesnittlogikken til brikken, og dette skjer umiddelbart etter lesing av linjen.

La oss nå se på de forskjellige typene dynamiske minnebrikker, og starter med system-DRAM, det vil si brikker designet for å brukes som hovedminne. I det innledende stadiet var disse asynkrone minnebrikker, hvis drift ikke er strengt knyttet til klokkepulsene til systembussen.

Asynkron dynamisk RAM. Asynkrone dynamiske RAM-brikker styres av RAS- og CAS-signaler, og deres drift er i prinsippet ikke direkte relatert til bussklokkepulser. Asynkront minne er preget av ekstra tid brukt på interaksjon mellom minnebrikker og kontrolleren. Så inn asynkron ordning RAS-signalet vil bli generert først etter at en klokkepuls kommer til kontrolleren og vil bli mottatt av minnebrikken etter en stund. Etter dette vil minnet produsere data, men kontrolleren vil kun kunne lese dem ved ankomst av neste klokkepuls, siden den må fungere synkront med resten av VM-enhetene. Dermed er det små forsinkelser under lese-/skrivesyklusen på grunn av at minnekontrolleren og minnekontrolleren venter.

DRAM-brikker. De første dynamiske minnebrikkene brukte den enkleste metoden for datautveksling, ofte kalt konvensjonell. Det tillot lesing og skriving av en minnelinje bare hver femte klokkesyklus . Trinnene i en slik prosedyre er beskrevet tidligere. Tradisjonell DRAM tilsvarer formelen 5-5-5-5. Mikrokretser av denne typen kunne operere ved frekvenser opp til 40 MHz, og på grunn av deres treghet (tilgangstiden var omtrent 120 ns), varte de ikke lenge.

FPMDRAM-brikker. Dynamiske RAM-brikker som implementerer FPM-modus er også tidlige typer DRAM. Essensen av regimet ble vist tidligere. Lesemønsteret for FPM DRAM er beskrevet av formelen 5-3-3-3 (14 klokkesykluser totalt). Bruken av en rask sidetilgangsordning reduserte tilgangstiden til 60 ns, noe som, tatt i betraktning muligheten til å operere ved høyere bussfrekvenser, førte til en økning i minneytelsen sammenlignet med tradisjonell DRAM med omtrent 70 %. Denne typen chip ble brukt i personlige datamaskiner til ca 1994.

EDO DRAM-brikker. Neste trinn i utviklingen av dynamisk RAM var ICer med hypersidetilgangsmodus(HRM, Hyper Page Mode), bedre kjent som EDO (Extended Data Output - utvidet dataoppbevaringstid ved utgangen). Hovedtrekket til teknologien er den økte tiden for datatilgjengelighet ved utgangen av mikrokretsen sammenlignet med FPM DRAM. I FPM DRAM-brikker forblir utdataene gyldige bare når CAS-signalet er aktivt, og det er grunnen til at den andre og påfølgende radtilgangen krever tre klokkesykluser: en CAS-bryter til aktiv tilstand, en dataleseklokke og en CAS-bryter til den inaktive tilstanden. I EDO DRAM, på den aktive (fallende) flanken til CAS-signalet, lagres dataene i et internt register, hvor de lagres en stund etter at neste aktive flanke av signalet kommer. Dette gjør at de lagrede dataene kan brukes når CAS allerede er i en inaktiv tilstand. Med andre ord, tidsparametere forbedres ved å eliminere sykluser med å vente på øyeblikket for datastabilisering ved utgangen av mikrokretsen.

Lesemønsteret til EDO DRAM er allerede 5-2-2-2, som er 20 % raskere enn FPM. Tilgangstid er ca. 30-40 ns. Det skal bemerkes at den maksimale systembussfrekvensen for EDO DRAM-brikker ikke bør overstige 66 MHz.

BEDO DRAM-brikker. EDO-teknologien har blitt forbedret av VIA Technologies. Den nye modifikasjonen av EDO er kjent som BEDO (Burst EDO). Det nye med metoden er at under den første tilgangen leses hele linjen til mikrokretsen, som inkluderer påfølgende ord i pakken. Den sekvensielle overføringen av ord (bytte kolonner) overvåkes automatisk av brikkens interne teller. Dette eliminerer behovet for å utstede adresser for alle celler i en pakke, men krever støtte fra ekstern logikk. Metoden lar deg redusere tiden for å lese de andre og påfølgende ordene med en annen klokkesyklus, på grunn av hvilken formelen har formen 5-1-1-1.

EDRAM-brikker. Mer rask versjon DRAM ble utviklet av Ramtrons divisjon, Enhanced Memory Systems. Teknologien er implementert i FPM, EDO og BEDO varianter. Brikken har en raskere kjerne og internt cache-minne. Tilgjengelighet av sistnevnte - hovedfunksjon teknologier. Bufferminnet er statisk minne (SRAM) med en kapasitet på 2048 biter. EDRAM-kjernen har 2048 kolonner, som hver er koblet til en intern cache. Når du får tilgang til en celle, leses hele raden (2048 biter) samtidig. Leselinjen legges inn i SRAM, og overføringen av informasjon til hurtigbufferminnet har praktisk talt ingen effekt på ytelsen, siden den skjer i én klokkesyklus. Når det gjøres ytterligere tilganger til celler som tilhører samme rad, hentes dataene fra det raskere cache-minnet. Den neste tilgangen til kjernen skjer ved tilgang til en celle som ikke er plassert i en linje som er lagret i brikkens cache-minne.

Teknologien er mest effektiv når sekvensiell lesing, det vil si når den gjennomsnittlige tilgangstiden for en brikke nærmer seg verdiene som er karakteristiske for statisk minne (omtrent 10 ns). Hovedproblemet er inkompatibilitet med kontrollere som brukes når du arbeider med andre typer DRAM.

Synkron dynamisk RAM. I synkron DRAM synkroniseres informasjonsutveksling av eksterne klokkesignaler og skjer på strengt definerte tidspunkter, noe som lar deg ta alt fra båndbredden til prosessor-minnebussen og unngå ventesykluser. Adresse- og kontrollinformasjon er registrert i minnet IC. Deretter vil responsen til mikrokretsen skje gjennom et klart definert antall klokkepulser, og prosessoren kan bruke denne tiden til andre handlinger som ikke er relatert til minnetilgang. I tilfelle av synkront dynamisk minne, i stedet for varigheten av tilgangssyklusen, snakker de om den minste tillatte perioden klokkefrekvens, og vi snakker allerede om en tid i størrelsesorden 8-10 ns.

SDRAM-brikker. Forkortelsen SDRAM (Synchronous DRAM) brukes for å referere til "vanlige" synkrone dynamiske RAM-brikker. De grunnleggende forskjellene mellom SDRAM og den asynkrone dynamiske RAM diskutert ovenfor kan reduseres til fire punkter:

· synkron metode overføre data til bussen;

· transportørmekanisme for pakkevideresending;

· bruk av flere (to eller fire) interne minnebanker;

· overføring av deler av funksjonene til minnekontrolleren til logikken til selve mikrokretsen.

Minnesynkronisitet lar minnekontrolleren "vite" når data er klare, og reduserer dermed kostnadene ved å vente og søke etter data. Siden data vises ved utgangen av IC-en samtidig med klokkepulser, forenkles interaksjonen mellom minne og andre VM-enheter.

I motsetning til BEDO, lar rørledningen pakkedata overføres klokke for klokke, slik at RAM-en kan fungere jevnt ved høyere frekvenser enn asynkron RAM. Fordelene med en rørledning er spesielt viktige ved overføring av lange pakker, men som ikke overskrider lengden på brikkelinjen.

En betydelig effekt oppnås ved å dele hele settet med celler i uavhengige interne arrays (banker). Dette lar deg kombinere tilgang til en celle i én bank med forberedelse til neste operasjon i de resterende bankene (lading av kontrollkretser og gjenoppretting av informasjon). Evnen til å holde flere linjer med minne åpent samtidig (fra forskjellige banker) bidrar også til å forbedre minneytelsen. Når du får tilgang til banker vekselvis, reduseres frekvensen av tilgang til hver av dem individuelt i forhold til antall banker, og SDRAM kan operere ved høyere frekvenser. Takket være den innebygde adressetelleren lar SDRAM, som BEDO DRAM, deg lese og skrive til batch-modus, og i SDRAM varierer pakkelengden og i batch-modus er det mulig å lese en hel minnelinje. IC kan karakteriseres ved formelen 5-1-1-1. Selv om formelen for denne typen dynamisk minne er den samme som BEDO, betyr muligheten til å operere ved høyere frekvenser at SDRAM med to banker med en bussklokkehastighet på 100 MHz nesten kan doble ytelsen til BEDO-minne.

DDR SDRAM-brikker. Et viktig steg i videreutviklingen av SDRAM-teknologien var DDR SDRAM (Double Data Rate SDRAM – SDRAM med dobbel dataoverføringshastighet). I motsetning til SDRAM ny modifikasjon gir data i burst-modus på begge kanter av synkroniseringspulsen, på grunn av dette dobles gjennomstrømningen. Det er flere DDR SDRAM-spesifikasjoner, avhengig av systembussens klokkehastighet: DDR266, DDR333, DDR400, DDR533. Dermed er toppbåndbredden til en DDR333-minnebrikke 2,7 GB/s, og for DDR400 er den 3,2 GB/s. DDR SDRAM er for tiden den vanligste typen dynamisk minne i personlige VM-er.

RDRAM, DRDRAM mikrokretser. De mest åpenbare måtene å øke effektiviteten til en prosessor med minne på er å øke bussens klokkefrekvens eller samplingsbredden (antall samtidig overførte biter). Dessverre møter forsøk på å kombinere begge alternativene betydelige tekniske vanskeligheter (ettersom frekvensen øker, blir problemene med elektromagnetisk kompatibilitet verre; det blir vanskeligere å sikre at alle parallelt sendte informasjonsbiter kommer til forbrukeren samtidig). De fleste synkrone DRAM-er (SDRAM, DDR) bruker bred sampling (64 bits) ved en begrenset bussfrekvens.

En fundamentalt annerledes tilnærming til å bygge DRAM ble foreslått av Rambus i 1997. Den fokuserer på å øke klokkehastigheten til 400 MHz samtidig som den reduserer prøvebredden til 16 biter. Det nye minnet er kjent som RDRAM (Rambus Direct RAM). Det finnes flere varianter av denne teknologien: Base, Concurrent og Direct. I alt utføres klokking på begge kanter av klokkesignaler (som i DDR), på grunn av hvilken den resulterende frekvensen er henholdsvis 500-600, 600-700 og 800 MHz. De to første alternativene er nesten identiske, men endringene i Direct Rambus (DRDRAM) teknologi er ganske betydelige.

Først, la oss se på de grunnleggende punktene i RDRAM-teknologi, og fokuserer hovedsakelig på den mer moderne versjonen - DRDRAM. Hovedforskjellen fra andre typer DRAM er originalt system datautveksling mellom kjernen og minnekontrolleren, som er basert på den såkalte "Rambus-kanalen", ved bruk av en asynkron blokk-orientert protokoll. På det logiske nivået overføres informasjon mellom kontrolleren og minnet i pakker.

Det er tre typer pakker: datapakker, radpakker og kolonnepakker. Pakker med rader og kolonner brukes til å overføre kommandoer fra minnekontrolleren for å kontrollere henholdsvis radene og kolonnene i rekken av lagringselementer. Disse kommandoene erstatter konvensjonelt system mikrokretskontroll ved hjelp av RAS-, CAS-, WE- og CS-signaler.

GE-matrisen er delt inn i banker. Antallet deres i en krystall med en kapasitet på 64 Mbit er 8 uavhengige eller 16 doble banker. I dual bank^ deler bankparet felles lese-/skriveforsterkere. Den interne kjernen i brikken har en 128-bits databuss, som gjør at 16 byte kan overføres til hver kolonneadresse. Ved opptak kan du bruke en maske der hver bit tilsvarer én byte i pakken. Ved å bruke masken kan du spesifisere hvor mange byte av pakken og hvilke byte som skal skrives til minnet.

Data-, rad- og kolonnelinjene i kanalen er helt uavhengige, så radkommandoer, kolonnekommandoer og data kan overføres samtidig, og for forskjellige banker av brikken. Kolonnepakker inneholder to felt og sendes over fem linjer. Det første feltet spesifiserer hovedskrive- eller leseoperasjonen. Det andre feltet inneholder enten en indikasjon på bruken av en postmaske (selve masken sendes over datalinjene), eller en utvidet operasjonskode som definerer et alternativ for hovedoperasjonen. Strengepakker er delt inn i kommandoer for aktivering, kansellering, regenerering og strømmodus. Tre linjer er tildelt for overføring av strengpakker.

Skriveoperasjonen kan umiddelbart følge avlesningen - bare en forsinkelse er nødvendig for tiden signalet går gjennom kanalen (fra 2,5 til 30 ns avhengig av lengden på kanalen). For å utjevne forsinkelser i overføringen av individuelle biter av den overførte koden, må lederne på brettet plasseres strengt parallelt, ha samme lengde (lengden på linjene bør ikke overstige 12 cm) og oppfylle strenge krav definert av utvikleren .

Hver skriving i kanalen kan pipelineres, med den første datapakken som har en latens på 50 ns, og de gjenværende lese-/skriveoperasjonene skjer kontinuerlig (latens introduseres kun når man skifter fra en skrive- til en leseoperasjon, og omvendt).

Tilgjengelige publikasjoner nevnes Intel fungerer og Rambus på en ny versjon av RDRAM kalt nDRAM som vil støtte dataoverføringshastigheter opp til 1600 MHz.

SLDRAM-brikker. En potensiell konkurrent til RDRAM som minnearkitekturstandard for fremtidige personlige VM-er er en ny type dynamisk RAM utviklet av SyncLink Consortium, et konsortium av VM-produsenter, kjent under forkortelsen SLDRAM. I motsetning til RDRAM, hvis teknologi er eiendommen til Rambus og Intel, er denne standarden åpen. På systemnivå teknologiene er veldig like. Data og kommandoer fra kontrolleren til minnet og tilbake til SLDRAM overføres i pakker med 4 eller 8 meldinger. Kommandoer, adresse og styresignaler sendes over en ensrettet 10-bits kommandobuss. Lese- og skrivedata overføres over en toveis 18-bits databuss. Begge bussene kjører med samme frekvens. Foreløpig er denne frekvensen fortsatt 200 MHz, som takket være DDR-teknologi tilsvarer 400 MHz. De neste generasjonene av SLDRAM bør operere ved frekvenser på 400 MHz og høyere, det vil si gi en effektiv frekvens på mer enn 800 MHz.

Opptil 8 minnebrikker kan kobles til én kontroller. For å unngå forsinkelser i signaler fra brikker lenger unna kontrolleren, bestemmes tidskarakteristikkene for hver brikke og føres inn i kontrollregisteret når strømmen slås på.

ESDRAM-brikker. Dette er en synkron versjon av EDRAM som bruker de samme teknikkene for å redusere tilgangstiden. En skriveoperasjon, i motsetning til en leseoperasjon, omgår hurtigbufferen, noe som øker ESDRAM-ytelsen når lesing gjenopptas fra en linje som allerede er i hurtigbufferen. Takket være tilstedeværelsen av to banker i brikken, minimeres nedetid på grunn av forberedelse til lese-/skriveoperasjoner. Ulempene med mikrokretsen under vurdering er de samme som for EDRAM - kontrolleren er mer kompleks, siden den må lese evnen til å forberede seg på å lese en ny kjernelinje inn i cache-minnet. I tillegg, med en vilkårlig sekvens av adresser, brukes cache-minnet ineffektivt.

CDRAM-brikker. Denne typen RAM ble utviklet av Mitsubishi Corporation, og den kan betraktes som en revidert versjon av ESDRAM, fri for noen av dens ufullkommenheter. Kapasiteten til hurtigbufferminnet og prinsippet om å plassere data i det er endret. Kapasiteten til en enkelt hurtigbufferblokk er redusert til 128 biter, slik at 16-kilobit-hurtigbufferen samtidig kan lagre kopier av 128 minneplasseringer, noe som muliggjør mer effektiv bruk av hurtigbufferminnet. Utskifting av den første minneseksjonen plassert i hurtigbufferen begynner først etter at den siste (128.) blokken er fylt. Adkomstmidlene har også endret seg. Dermed bruker brikken separate adressebusser for den statiske cachen og den dynamiske kjernen. Overføring av data fra den dynamiske kjernen til cache-minnet kombineres med utsendelse av data til bussen, så hyppige, men korte overføringer reduserer ikke ytelsen til IC når du leser store mengder informasjon fra minnet og setter CDRAM på linje med ESDRAM, og når du leser på selektive adresser vinner CDRAM klart. Det skal imidlertid bemerkes at endringene ovenfor førte til enda større kompleksitet for minnekontrolleren.

Det er mye mer dynamisk minne i en datamaskin enn statisk minne, siden DRAM brukes som hovedminnet til VM. Som SRAM består dynamisk minne av en kjerne (en rekke elektroniske enheter) og grensesnittlogikk (bufferregistre, dataleseforsterkere, regenereringskretser, etc.). Selv om antallet typer DRAM allerede har oversteget to dusin, er kjernene deres organisert nesten identisk. Hovedforskjellene er relatert til grensesnittlogikken, og disse forskjellene skyldes også anvendelsesområdet for mikrokretsene - i tillegg til hovedminnet til VM, er dynamiske minne-IC-er inkludert, for eksempel i videoadaptere. Klassifiseringen av dynamiske minnebrikker er vist i fig. 5.10.

For å evaluere forskjellene mellom typer DRAM, la oss først se på algoritmen for å jobbe med dynamisk minne. For dette vil vi bruke fig. 5.6.

I motsetning til SRAM, blir adressen til en DRAM-celle overført til brikken i to trinn, først kolonneadressen og deretter radadressen, som gjør det mulig å redusere antall adressebuss-pinner med omtrent det halve, redusere størrelsen på saken. og plasser et større antall brikker på hovedkortet. Dette fører selvfølgelig til en nedgang i ytelsen, siden det tar dobbelt så lang tid å overføre adressen. For å indikere hvilken del av adressen som sendes på et bestemt tidspunkt, brukes to hjelpesignaler RAS og CAS. Ved tilgang til en minnecelle settes adressebussen til adressen til raden. Etter at prosessene på bussen har stabilisert seg, påføres RAS-signalet og adressen skrives til det interne registeret til brikken

Ris. 5.10. Klassifisering av dynamisk RAM: a - brikker for hovedminne; b - brikker for videoadaptere

hukommelse. Adressebussen settes så til kolonneadressen og CAS-signalet sendes. Avhengig av tilstanden til WE-linjen, leses data fra cellen eller skrives til cellen (dataene må plasseres på databussen før skriving). Intervallet mellom å sette adressen og utstede RAS-signalet (eller CAS-signalet) bestemmes av de tekniske egenskapene til mikrokretsen, men vanligvis settes adressen i en syklus av systembussen, og kontrollsignalet i den neste. For å lese eller skrive én celle med dynamisk RAM, kreves det derfor fem klokkesykluser, der følgende skjer: utstede en radadresse, utstede et RAS-signal, utstede en kolonneadresse, utstede et CAS-signal, utføre en lese-/skriveoperasjon (i statisk minne tar prosedyren bare to til tre tiltak).

Du bør også huske behovet for dataregenerering. Men sammen med den naturlige utladningen av kondensatoren, fører den elektroniske enheten også til tap av ladning over tid ved lesing av data fra DRAM, så etter hver leseoperasjon må dataene gjenopprettes. Dette oppnås ved å skrive de samme dataene på nytt umiddelbart etter lesing. Når du leser informasjon fra en celle, sendes faktisk dataene til hele den valgte raden ut samtidig, men bare de som er i interessekolonnen brukes, og resten blir ignorert. Dermed resulterer en leseoperasjon fra én celle i ødeleggelse av hele radens data og må gjenopprettes. Dataregenerering etter lesing utføres automatisk av grensesnittlogikken til brikken, og dette skjer umiddelbart etter lesing av linjen.

La oss nå se på de forskjellige typene dynamiske minnebrikker, og starter med system-DRAM, det vil si brikker designet for å brukes som hovedminne. I det innledende stadiet var disse asynkrone minnebrikker, hvis drift ikke er strengt knyttet til klokkepulsene til systembussen.

Asynkron dynamisk RAM. Asynkrone dynamiske RAM-brikker styres av RAS- og CAS-signaler, og deres drift er i prinsippet ikke direkte relatert til bussklokkepulser. Asynkront minne er preget av ekstra tid brukt på samspillet mellom minnebrikker og kontrolleren. I en asynkron krets vil således RAS-signalet genereres først etter at en klokkepuls kommer til kontrolleren og vil bli oppfattet av minnebrikken etter noen tid. tid. Etter dette vil minnet produsere data, men kontrolleren vil kun kunne lese dem ved ankomst av neste klokkepuls, siden den må fungere synkront med resten av VM-enhetene. Dermed er det små forsinkelser under lese-/skrivesyklusen på grunn av at minnekontrolleren og minnekontrolleren venter.

MikrokretserDRAM. De første dynamiske minnebrikkene brukte den enkleste metoden for datautveksling, ofte kalt konvensjonell. Den tillot lesing og skriving av en minnelinje kun hver femte klokkesyklus (fig. 5.11, EN). Trinnene i en slik prosedyre er beskrevet tidligere. Tradisjonell DRAM tilsvarer formelen 5-5-5-5. Mikrokretser av denne typen kunne operere ved frekvenser opp til 40 MHz, og på grunn av deres treghet (tilgangstiden var omtrent 120 sekunder), varte de ikke lenge.

MikrokretserFPM DRAM. Dynamiske RAM-brikker som implementerer FPM-modus er også tidlige typer DRAM. Essensen av regimet ble vist tidligere. Lesekretsen for FPM DRAM (fig. 5.11, b) er beskrevet med formelen 5-3-3-3 (14 klokkesykluser totalt). Bruken av en rask sidetilgangsordning har redusert tilgangstiden til 60 sekunder, noe som, tatt i betraktning muligheten til å operere på høyere bussfrekvenser, har ført til en økning i minneytelsen sammenlignet med tradisjonell DRAM med omtrent 70 %. Denne typen brikke ble brukt i personlige datamaskiner frem til rundt 1994.

MikrokretserEDO DRAM. Neste trinn i utviklingen av dynamisk RAM var ICer med hypersidemodus, tilgang(HRM, Hyper Page Mode), bedre kjent som EDO (Extended Data Output - utvidet dataoppbevaringstid ved utgangen). Hovedtrekket til teknologien er den økte tiden for datatilgjengelighet ved utgangen av mikrokretsen sammenlignet med FPM DRAM. I FPM DRAM-brikker forblir utdataene gyldige bare når CAS-signalet er aktivt, og det er grunnen til at den andre og påfølgende radtilgangen krever tre klokkesykluser: en CAS-bryter til aktiv tilstand, en dataleseklokke og en CAS-bryter til den inaktive tilstanden. I EDO DRAM, på den aktive (fallende) flanken til CAS-signalet, lagres dataene i et internt register, hvor de lagres en stund etter at neste aktive flanke av signalet kommer. Dette gjør at de lagrede dataene kan brukes når CAS allerede er i en inaktiv tilstand (fig. 5.11, V)

Med andre ord, tidsparametere forbedres ved å eliminere sykluser med å vente på øyeblikket for datastabilisering ved utgangen av mikrokretsen.

Lesemønsteret til EDO DRAM er allerede 5-2-2-2, som er 20 % raskere enn FPM. Tilgangstid er ca. 30-40 ns. Det skal bemerkes at den maksimale systembussfrekvensen for EDO DRAM-brikker ikke bør overstige 66 MHz.

MikrokretserBEDO DRAM. EDO-teknologien har blitt forbedret av VIA Technologies. Den nye modifikasjonen av EDO er kjent som BEDO (Burst EDO). Det nye med metoden er at under den første tilgangen leses hele linjen til mikrokretsen, som inkluderer påfølgende ord i pakken. Den sekvensielle overføringen av ord (bytte kolonner) overvåkes automatisk av brikkens interne teller. Dette eliminerer behovet for å utstede adresser for alle celler i en pakke, men krever støtte fra ekstern logikk. Metoden lar deg redusere tiden for å lese de andre og påfølgende ordene med en annen klokkesyklus (fig. 5.11, d), på grunn av hvilken formelen har formen 5-1-1-1.

5.11. Tidsdiagrammer for ulike typer asynkront dynamisk minne med en pakkelengde på fire ord: a - tradisjonell DRAM; b - FPM FRAM; V- EDO DRAM;

G - BEDO DRAM

MikrokretserEDRAM. En raskere versjon av DRAM ble utviklet av Ramtrons datterselskap, Enhanced Memory Systems. Teknologien er implementert i FPM, EDO og BEDO varianter. Brikken har en raskere kjerne og internt cache-minne. Tilstedeværelsen av sistnevnte er hovedtrekket i teknologien. Bufferminnet er statisk minne (SRAM) med en kapasitet på 2048 biter. EDRAM-kjernen har 2048 kolonner, som hver er koblet til en intern cache. Når du får tilgang til en celle, leses hele raden (2048 biter) samtidig. Leselinjen legges inn i SRAM, og overføringen av informasjon til cache-minnet har praktisk talt ingen effekt på ytelsen siden den skjer i én klokkesyklus. Når det gjøres ytterligere tilganger til celler som tilhører samme rad, hentes dataene fra det raskere cache-minnet. Den neste tilgangen til kjernen skjer ved tilgang til en celle som ikke er plassert i en linje som er lagret i bufferminnet til brikken.

Teknologien er mest effektiv når du leser sekvensielt, det vil si når den gjennomsnittlige tilgangstiden for en brikke nærmer seg verdiene som er karakteristiske for statisk minne (ca. 10 ns). Hovedproblemet er inkompatibilitet med kontrollere som brukes når du arbeider med andre typer DRAM

Synkron dynamisk RAM. I synkron DRAM synkroniseres informasjonsutveksling av eksterne klokkesignaler og skjer på strengt definerte tidspunkter, noe som lar deg ta alt fra båndbredden til prosessor-minnebussen og unngå ventesykluser. Adresse og kontrollinformasjon er registrert i minnet IC. Deretter vil responsen til mikrokretsen skje gjennom et klart definert antall klokkepulser, og prosessoren kan bruke denne tiden til andre handlinger som ikke er relatert til minnetilgang. Når det gjelder synkront dynamisk minne, i stedet for varigheten av tilgangssyklusen, snakker de om den minste tillatte perioden for klokkefrekvensen, og vi snakker allerede om en tid i størrelsesorden 8-10 ns.

MikrokretserSDRAM. Forkortelsen SDRAM (Synchronous DRAM) brukes for å referere til "vanlige" synkrone dynamiske RAM-brikker. De grunnleggende forskjellene mellom SDRAM og den asynkrone dynamiske RAM diskutert ovenfor kan reduseres til fire punkter:

Synkron metode for dataoverføring til bussen;

Transportørmekanisme for pakkevideresending;

Bruk av flere (to eller fire) interne minnebanker;

Overføring av deler av funksjonene til minnekontrolleren til logikken til selve mikrokretsen.

Minnesynkronisitet lar minnekontrolleren "vite" når data er klare, og reduserer dermed kostnadene ved å vente og søke etter data. Siden data vises ved utgangen av IC-en samtidig med klokkepulser, forenkles interaksjonen mellom minne og andre VM-enheter.

I motsetning til BEDO, tillater rørledningen pakkedata å overføres klokke for klokke, takket være at RAM kan fungere uavbrutt ved høyere frekvenser enn asynkron RAM. Fordelene med en rørledning er spesielt viktige ved overføring av lange pakker, men som ikke overskrider lengden på brikkelinjen.

En betydelig effekt oppnås ved å dele hele settet med celler i uavhengige interne arrays (banker). Dette lar deg kombinere tilgang til en celle i én bank med forberedelse til neste operasjon i de resterende bankene (lading av kontrollkretser og gjenoppretting av informasjon). Evnen til å holde flere linjer med minne åpent samtidig (fra forskjellige banker) bidrar også til å forbedre minneytelsen. Når du får tilgang til banker vekselvis, reduseres frekvensen av tilgang til hver av dem individuelt i forhold til antall banker, og SDRAM kan operere ved høyere frekvenser. Takket være den innebygde adressetelleren tillater SDRAM, som BEDO DRAM, lesing og skriving i burst-modus, og i SDRAM varierer burst-lengden og i burst-modus er det mulig å lese en hel minnelinje. IC kan karakteriseres ved formelen 5-1-1-1. Til tross for at formelen for denne typen dynamisk minne er den samme som BEDO, betyr muligheten til å operere ved høyere frekvenser at SDRAM med to 6 banker med en bussklokkehastighet på 100 MHz nesten kan doble ytelsen til BEDO-minne .

MikrokretserDDR SDRAM. Et viktig steg i videreutviklingen av SDRAM-teknologien var DDR SDRAM (Double Data Rate SDRAM – SDRAM med dobbel dataoverføringshastighet). I motsetning til SDRAM, produserer den nye modifikasjonen data i burst-modus på begge kanter av synkroniseringspulsen, på grunn av dette dobles gjennomstrømningen. Det er flere DDR SDRAM-spesifikasjoner, avhengig av systembussens klokkehastighet: DDR266, DDR333, DDR400, DDR533. Dermed er toppbåndbredden til en DDR333-minnebrikke 2,7 GB/s, og for DDR400 er den 3,2 GB/s. DDR SDRAM er for tiden den vanligste typen dynamisk minne i personlige VM-er.

MikrokretserRDRAM, DRDRAM. De mest åpenbare måtene å øke effektiviteten til en prosessor med minne på er å øke bussens klokkefrekvens eller samplingsbredden (antall samtidig overførte biter). Dessverre møter forsøk på å kombinere begge alternativene betydelige tekniske vanskeligheter (ettersom frekvensen øker, blir problemene med elektromagnetisk kompatibilitet verre; det blir vanskeligere å sikre at alle parallelt sendte informasjonsbiter kommer til forbrukeren samtidig). De fleste synkrone DRAM-er (SDRAM, DDR) bruker bred sampling (64 bits) ved en begrenset bussfrekvens.

En fundamentalt annerledes tilnærming til å bygge DRAM ble foreslått av Rambus i 1997. Den fokuserer på å øke klokkehastigheten til 400 MHz samtidig som den reduserer prøvebredden til 16 biter. Nytt minne kjent som RDRAM (Rambus Direct RAM). Det finnes flere varianter av denne teknologien: Base, Concurrent og Direct. I alt utføres klokking på begge kanter av klokkesignaler (som i DDR), på grunn av hvilken den resulterende frekvensen er henholdsvis 500-600, 600-700 og 800 MHz. De to første alternativene er nesten identiske, men endringene i Direct Rambus-teknologien er ganske betydelige.

Først, la oss se på de grunnleggende punktene i RDRAM-teknologi, og fokuserer hovedsakelig på den mer moderne versjonen - DRDRAM. Hovedforskjellen fra andre typer DRAM er det originale datautvekslingssystemet mellom kjernen og minnekontrolleren, som er basert på den såkalte "Rambus-kanalen" ved bruk av en asynkron blokkorientert protokoll. På det logiske nivået overføres informasjon mellom kontrolleren og minnet i pakker.

Det er tre typer pakker: datapakker, radpakker og kolonnepakker. Pakker med rader og kolonner brukes til å overføre kommandoer fra minnekontrolleren for å kontrollere henholdsvis radene og kolonnene i rekken av lagringselementer. Disse kommandoene erstatter det konvensjonelle chipkontrollsystemet som bruker RAS-, CAS-, WE- og CS-signaler.

GE-matrisen er delt inn i banker. Antallet deres i en krystall med en kapasitet på 64 Mbit er 8 uavhengige eller 16 doble banker. I doble banker deler bankparet felles lese-/skriveforsterkere. Den interne kjernen i brikken har en 128-bits databuss, som gjør at 16 byte kan overføres til hver kolonneadresse. Ved opptak kan du bruke en maske der hver bit tilsvarer én byte av pakken. Ved å bruke masken kan du spesifisere hvor mange byte av pakken og hvilke byte som skal skrives til minnet.

Data-, rad- og kolonnelinjene i kanalen er helt uavhengige, så radkommandoer, kolonnekommandoer og data kan overføres samtidig, og for forskjellige banker av brikken. Kolonnepakker inneholder to felt og sendes over fem linjer. Det første feltet spesifiserer hovedskrive- eller leseoperasjonen. Det andre feltet inneholder enten en indikasjon på bruken av en postmaske (selve masken sendes over datalinjene), eller en utvidet operasjonskode som definerer et alternativ for hovedoperasjonen. Strengepakker er delt inn i kommandoer for aktivering, kansellering, regenerering og strømmodus. Tre linjer er tildelt for overføring av strengpakker.

Skriveoperasjonen kan umiddelbart følge lesingen - bare en forsinkelse er nødvendig for tiden signalet går gjennom kanalen (fra 2,5 til 30, ikke avhengig av lengden på kanalen). For å utjevne forsinkelser i overføringen av individuelle biter av den overførte koden, må lederne på brettet plasseres strengt parallelt, ha samme lengde (lengden på linjene bør ikke overstige 12 cm) og oppfylle strenge krav definert av utvikleren .

Hver skriving i kanalen kan pipelineres, med den første datapakken som har en latens på 50 ns, og de gjenværende lese-/skriveoperasjonene skjer kontinuerlig (latens introduseres kun når man skifter fra en skrive- til en leseoperasjon, og omvendt).

Tilgjengelige publikasjoner nevner arbeidet til Intel og Rambus med en ny versjon av RDRAM, kalt nDRAM, som vil støtte dataoverføring ved frekvenser opp til 1600 MHz.

MikrokretserSLDRAM. En potensiell konkurrent til RDRAM som minnearkitekturstandard for fremtidige personlige VM-er er en ny type dynamisk RAM utviklet av SyncLm Consortium, et konsortium av VM-produsenter, kjent under forkortelsen SLDRAM. I motsetning til RDRAM, hvis teknologi er eiendommen til Rambus og Intel, denne standarden- åpen. På systemnivå er teknologiene veldig like. Data og kommandoer fra kontrolleren til minnet og tilbake til SLDRAM overføres i pakker på n eller 8 pakker. Kommandoer, adresse og styresignaler sendes over en ensrettet 10-bits kommandobuss. Lese- og skrivedata leveres over en toveis 18-bits databuss. Begge bussene kjører med samme frekvens. Foreløpig er denne frekvensen fortsatt 200 MHz, som takket være DDR-teknologi tilsvarer 400 MHz. De neste generasjonene av SLDRAM bør operere ved frekvenser på 400 MHz og høyere, det vil si gi en effektiv frekvens på mer enn 800 MHz.

Opptil 8 minnebrikker kan kobles til én kontroller. For å unngå forsinkelser i signaler fra brikker lenger unna kontrolleren, bestemmes tidskarakteristikkene for hver brikke og føres inn i kontrollregisteret når strømmen slås på.

MikrokretserESDRAM. Dette er en synkron versjon av EDRAM som bruker de samme teknikkene for å redusere tilgangstiden. En skriveoperasjon, i motsetning til en skriveoperasjon, omgår hurtigbufferen, noe som øker FSDRAM-ytelsen når du gjenopptar lesing fra en linje som allerede er i hurtigbufferen. Takket være tilstedeværelsen av to banker i brikken, minimeres nedetid på grunn av forberedelse til lese-/skriveoperasjoner. Ulempene med mikrokretsen under vurdering er de samme som for EDRAM - komplikasjonen til kontrolleren, siden den må ta hensyn til muligheten for å forberede seg på å lese en ny kjernelinje inn i hurtigbufferminnet. I tillegg, med en vilkårlig sekvens av adresser, brukes cache-minnet ineffektivt.

MikrokretserCDRAM. Denne typen RAM ble utviklet av Mitsubishi Corporation, og den kan betraktes som en revidert versjon av ESDRAM, fri for noen av dens ufullkommenheter. Kapasiteten til hurtigbufferminnet og prinsippet om å plassere data i det er endret. Kapasiteten til en enkelt hurtigbufferblokk er redusert til 128 biter, slik at 16-kilobit-hurtigbufferen samtidig kan lagre kopier av 128 minneplasseringer, noe som muliggjør mer effektiv bruk av hurtigbufferminnet. Utskifting av den første minneseksjonen plassert i hurtigbufferen begynner først etter at den siste (128.) blokken er fylt. Adkomstmidlene har også endret seg. Dermed bruker brikken separate adressebusser for den statiske cachen og den dynamiske kjernen. Overføring av data fra den dynamiske kjernen til cache-minnet kombineres med utsendelse av data til bussen, så hyppige, men korte overføringer reduserer ikke ytelsen til IC når du leser store mengder informasjon fra minnet og setter CDRAM på linje med ESDRAM, og når du leser på selektive adresser vinner CDRAM klart. Det skal imidlertid bemerkes at endringene ovenfor førte til enda større kompleksitet for minnekontrolleren.

Det er mye mer dynamisk minne i en datamaskin enn statisk minne, siden DRAM brukes som hovedminnet til VM. Som SRAM består dynamisk minne av en kjerne (en rekke elektroniske enheter) og grensesnittlogikk (bufferregistre, dataleseforsterkere, regenereringskretser, etc.).

I motsetning til SRAM, blir adressen til en DRAM-celle overført til brikken i to trinn - først kolonneadressen, og deretter raden, som gjør det mulig å redusere antall adressebusspinner med omtrent det halve, redusere størrelsen på saken. og plasser et større antall brikker på hovedkortet. Dette fører selvfølgelig til en nedgang i ytelsen, siden det tar dobbelt så lang tid å overføre adressen. For å indikere hvilken del av adressen som sendes på et bestemt tidspunkt, brukes to hjelpesignaler RAS og CAS. Ved tilgang til en minnecelle settes adressebussen til adressen til raden. Etter at prosessene på bussen har stabilisert seg, tilføres RAS-signalet og adressen skrives til det interne registeret til minnebrikken. Adressebussen settes så til kolonneadressen og CAS-signalet sendes. Avhengig av tilstanden til WE-linjen, leses data fra cellen eller skrives til cellen (dataene må plasseres på databussen før skriving). Intervallet mellom å sette adressen og utstede RAS-signalet (eller CAS-signalet) bestemmes av de tekniske egenskapene til mikrokretsen, men vanligvis settes adressen i en syklus av systembussen, og kontrollsignalet i den neste. For å lese eller skrive én celle med dynamisk RAM, kreves det derfor fem klokkesykluser, der følgende skjer: utstede en radadresse, utstede et RAS-signal, utstede en kolonneadresse, utstede et CAS-signal, utføre en lese-/skriveoperasjon (i statisk minne tar prosedyren bare to til tre tiltak).

Ris. 5.10. Klassifisering av dynamisk RAM: a - brikker for hovedminne; b- brikker for videoadaptere

Du bør også huske behovet for dataregenerering. Men sammen med den naturlige utladningen av kondensatoren, fører den elektroniske enheten også til tap av ladning over tid ved lesing av data fra DRAM, så etter hver leseoperasjon må dataene gjenopprettes. Dette oppnås ved å skrive de samme dataene på nytt umiddelbart etter lesing. Når du leser informasjon fra en celle, sendes faktisk dataene til hele den valgte raden ut samtidig, men bare de som er i interessekolonnen brukes, og resten blir ignorert. Dermed ødelegger en leseoperasjon fra en enkelt celle hele radens data og må gjenopprettes. Dataregenerering etter lesing utføres automatisk av grensesnittlogikken til brikken, og dette skjer umiddelbart etter lesing av linjen. La oss nå se på de forskjellige typene dynamiske minnebrikker, og starter med system-DRAM, det vil si brikker designet for å brukes som hovedminne. I det innledende stadiet var disse asynkrone minnebrikker, hvis drift ikke er strengt knyttet til klokkepulsene til systembussen.

Asynkron dynamisk RAM. Asynkrone dynamiske RAM-brikker styres av RAS- og CAS-signaler, og deres drift er i prinsippet ikke direkte relatert til bussklokkepulser. Asynkront minne er preget av ekstra tid brukt på interaksjon mellom minnebrikker og kontrolleren. I en asynkron krets vil således RAS-signalet genereres først etter at en klokkepuls kommer til kontrolleren og vil bli oppfattet av minnebrikken etter en tid. Etter dette vil minnet produsere data, men kontrolleren vil kun kunne lese dem ved ankomst av neste klokkepuls, siden den må fungere synkront med resten av VM-enhetene. Dermed er det små forsinkelser under lese-/skrivesyklusen på grunn av at minnekontrolleren og minnekontrolleren venter.

DRAM-brikker. De første dynamiske minnebrikkene brukte den enkleste metoden for datautveksling, ofte kalt konvensjonell. Den tillot lesing og skriving av en minnelinje kun hver femte klokkesyklus (fig. 5.11, EN). Trinnene i en slik prosedyre er beskrevet tidligere. Tradisjonell DRAM tilsvarer formelen 5-5-5-5. Mikrokretser av denne typen kunne operere ved frekvenser opp til 40 MHz, og på grunn av deres treghet (tilgangstiden var omtrent 120 sekunder), varte de ikke lenge.

FPMDRAM-brikker. Dynamiske RAM-brikker som implementerer FPM-modus er også tidlige typer DRAM. Essensen av regimet ble vist tidligere. Lesekrets for FPM DRAM (fig. 5.11, 6) beskrevet av formelen 5-3-3-3 (14 stolper totalt). Bruken av en rask sidetilgangsordning reduserte tilgangstiden til 60 sekunder, noe som, tatt i betraktning muligheten til å operere ved høyere bussfrekvenser, førte til en økning i minneytelsen sammenlignet med tradisjonell DRAM med omtrent 70 %. Denne typen brikke ble brukt i personlige datamaskiner frem til rundt 1994.

EDO DRAM-brikker. Neste trinn i utviklingen av dynamisk RAM var ICer med hypersidetilgangsmodus(HRM, Hyper Page Mode), bedre kjent som EDO (Extended Data Output - utvidet dataoppbevaringstid ved utgangen). Hovedtrekket til teknologien er den økte tiden for datatilgjengelighet ved utgangen av mikrokretsen sammenlignet med FPM DRAM. I FPM DRAM-brikker forblir utdataene gyldige bare når CAS-signalet er aktivt, og det er grunnen til at den andre og påfølgende radtilgangen krever tre klokkesykluser: en CAS-bryter til aktiv tilstand, en dataleseklokke og en CAS-bryter til den inaktive tilstanden. I EDO DRAM, på den aktive (fallende) flanken til CAS-signalet, lagres dataene i et internt register, hvor de lagres en stund etter at neste aktive flanke av signalet kommer. Dette lar deg bruke lagrede data når CAS allerede er i en inaktiv tilstand (fig. 5.11, b). Med andre ord, tidsparametere forbedres ved å eliminere sykluser med å vente på øyeblikket for datastabilisering ved utgangen av mikrokretsen.

Lesemønsteret til EDO DRAM er allerede 5-2-2-2, som er 20 % raskere enn FPM. Tilgangstiden er ca. 30-40 sekunder. Det skal bemerkes at den maksimale systembussfrekvensen for EDO DRAM-brikker ikke bør overstige 66 MHz.

BEDO DRAM-brikker. EDO-teknologien har blitt forbedret av VIA Technologies. Den nye modifikasjonen av EDO er kjent som BEDO (Burst EDO). Det nye med metoden er at under den første tilgangen leses hele linjen til mikrokretsen, som inkluderer påfølgende ord i pakken. Den sekvensielle overføringen av ord (bytte kolonner) overvåkes automatisk av brikkens interne teller. Dette eliminerer behovet for å utstede adresser for alle celler i en pakke, men krever støtte fra ekstern logikk. Metoden lar deg redusere tiden for lesing av de andre og påfølgende ordene med en annen klokkesyklus (fig. 5.11, G), på grunn av hvilken formelen har formen 5-1-1-1.

EDRAM-brikker. En raskere versjon av DRAM ble utviklet av Ramtrons datterselskap, Enhanced Memory Systems. Teknologien er implementert i FPM, EDO og BEDO varianter. Brikken har en raskere kjerne og internt cache-minne. Tilstedeværelsen av sistnevnte er hovedtrekket i teknologien. Bufferminnet er statisk minne (SRAM) med en kapasitet på 2048 biter. EDRAM-kjernen har 2048 kolonner, som hver er koblet til en intern cache. Når du får tilgang til en celle, leses hele raden (2048 biter) samtidig. Leselinjen legges inn i SRAM, og overføringen av informasjon til hurtigbufferminnet har praktisk talt ingen effekt på ytelsen, siden den skjer i én klokkesyklus. Når det gjøres ytterligere tilganger til celler som tilhører samme rad, hentes dataene fra det raskere cache-minnet. Den neste tilgangen til kjernen skjer ved tilgang til en celle som ikke er plassert i en linje som er lagret i brikkens cache-minne.

Teknologien er mest effektiv når du leser sekvensielt, det vil si når den gjennomsnittlige tilgangstiden for en brikke nærmer seg verdiene som er karakteristiske for statisk minne (ca. 10 ns). Hovedproblemet er inkompatibilitet med kontrollere som brukes når du arbeider med andre typer DRAM.

Synkron dynamisk RAM. I synkron DRAM synkroniseres informasjonsutveksling av eksterne klokkesignaler og skjer på strengt definerte tidspunkter, noe som lar deg ta alt fra båndbredden til prosessor-minnebussen og unngå ventesykluser. Adresse- og kontrollinformasjon er registrert i minnet IC. Deretter vil responsen til mikrokretsen skje gjennom et klart definert antall klokkepulser, og prosessoren kan bruke denne tiden til andre handlinger som ikke er relatert til minnetilgang. Når det gjelder synkront dynamisk minne, i stedet for varigheten av tilgangssyklusen, snakker de om den minste tillatte perioden for klokkefrekvensen, og vi snakker allerede om en tid i størrelsesorden 8-10 ns.

SDRAM-brikker. Forkortelsen SDRAM (Synchronous DRAM) brukes for å referere til "vanlige" synkrone dynamiske RAM-brikker. De grunnleggende forskjellene mellom SDRAM og den asynkrone dynamiske RAM diskutert ovenfor kan reduseres til fire punkter:

synkron metode for dataoverføring til bussen;

transportørmekanisme for pakkevideresending;

bruk av flere (to eller fire) interne minnebanker;

overføre deler av funksjonene til minnekontrolleren til logikken til selve mikrokretsen.

Minnesynkronisitet lar minnekontrolleren "vite" når data er klare, og reduserer dermed kostnadene ved å vente og søke etter data. Siden data vises ved utgangen av IC-en samtidig med klokkepulser, forenkles interaksjonen mellom minne og andre VM-enheter.

I motsetning til BEDO, lar rørledningen pakkedata overføres klokke for klokke, slik at RAM-en kan fungere jevnt ved høyere frekvenser enn asynkron RAM. Fordelene med en rørledning er spesielt viktige ved overføring av lange pakker, men som ikke overskrider lengden på brikkelinjen.

En betydelig effekt oppnås ved å dele hele settet med celler i uavhengige interne arrays (banker). Dette lar deg kombinere tilgang til en celle i én bank med forberedelse til neste operasjon i de resterende bankene (lading av kontrollkretser og gjenoppretting av informasjon). Evnen til å holde flere linjer med minne åpent samtidig (fra forskjellige banker) bidrar også til å forbedre minneytelsen. Når du får tilgang til banker vekselvis, reduseres frekvensen av tilgang til hver av dem individuelt i forhold til antall banker, og SDRAM kan operere ved høyere frekvenser. Takket være den innebygde adressetelleren tillater SDRAM, som BEDO DRAM, lesing og skriving i burst-modus, og i SDRAM varierer burst-lengden og i burst-modus er det mulig å lese en hel minnelinje. IC kan karakteriseres ved formelen 5-1-1-1. Selv om formelen for denne typen dynamisk minne er den samme som BEDO, betyr muligheten til å operere ved høyere frekvenser at SDRAM med to banker med en bussklokkehastighet på 100 MHz nesten kan doble ytelsen til BEDO-minne.

DDR SDRAM-brikker. Et viktig steg i videreutviklingen av SDRAM-teknologien var DDR SDRAM (Double Data Rate SDRAM – SDRAM med dobbel dataoverføringshastighet). I motsetning til SDRAM, produserer den nye modifikasjonen data i burst-modus på begge kanter av synkroniseringspulsen, på grunn av dette dobles gjennomstrømningen. Det er flere DDR SDRAM-spesifikasjoner, avhengig av systembussens klokkehastighet: DDR266, DDR333, DDR400, DDR533. Dermed er toppbåndbredden til en DDR333-minnebrikke 2,7 GB/s, og for DDR400 er den 3,2 GB/s. DDR SDRAM er for tiden den vanligste typen dynamisk minne i personlige VM-er.

RDRAM, DRDRAM mikrokretser. De mest åpenbare måtene å øke effektiviteten til en prosessor med minne på er å øke bussens klokkefrekvens eller samplingsbredden (antall samtidig overførte biter). Dessverre møter forsøk på å kombinere begge alternativene betydelige tekniske vanskeligheter (ettersom frekvensen øker, blir problemene med elektromagnetisk kompatibilitet verre; det blir vanskeligere å sikre at alle parallelt sendte informasjonsbiter kommer til forbrukeren samtidig). De fleste synkrone DRAM-er (SDRAM, DDR) bruker bred sampling (64 bits) ved en begrenset bussfrekvens.

En fundamentalt annerledes tilnærming til å bygge DRAM ble foreslått av Rambus i 1997. Den fokuserer på å øke klokkehastigheten til 400 MHz samtidig som den reduserer prøvebredden til 16 biter. Det nye minnet er kjent som RDRAM (Rambus Direct RAM). Det finnes flere varianter av denne teknologien: Base, Concurrent og Direct. I alt utføres klokking på begge kanter av klokkesignaler (som i DDR), på grunn av hvilken den resulterende frekvensen er henholdsvis 500-600, 600-700 og 800 MHz. De to første alternativene er nesten identiske, men endringene i Direct Rambus (DRDRAM) teknologi er ganske betydelige.

Først, la oss se på de grunnleggende punktene i RDRAM-teknologi, og fokuserer hovedsakelig på den mer moderne versjonen - DRDRAM. Hovedforskjellen fra andre typer DRAM er det originale datautvekslingssystemet mellom kjernen og minnekontrolleren, som er basert på den såkalte "Rambus-kanalen" ved bruk av en asynkron blokkorientert protokoll. På det logiske nivået overføres informasjon mellom kontrolleren og minnet i pakker.

Det er tre typer pakker: datapakker, radpakker og kolonnepakker. Pakker med rader og kolonner brukes til å overføre kommandoer fra minnekontrolleren for å kontrollere henholdsvis radene og kolonnene i rekken av lagringselementer. Disse kommandoene erstatter det konvensjonelle chipkontrollsystemet som bruker RAS-, CAS-, WE- og CS-signaler.

SLDRAM-brikker. En potensiell konkurrent til RDRAM som minnearkitekturstandard for fremtidige personlige VM-er er en ny type dynamisk RAM utviklet av SyncLink Consortium, et konsortium av VM-produsenter, kjent under forkortelsen SLDRAM. I motsetning til RDRAM, hvis teknologi er eiendommen til Rambus og Intel, er denne standarden åpen. På systemnivå er teknologiene veldig like. Data og kommandoer fra kontrolleren til minnet og tilbake til SLDRAM overføres i pakker med 4 eller 8 meldinger. Kommandoer, adresse og styresignaler sendes over en ensrettet 10-bits kommandobuss. Lese- og skrivedata overføres over en toveis 18-bits databuss. Begge bussene kjører med samme frekvens. Foreløpig er denne frekvensen fortsatt 200 MHz, som takket være DDR-teknologi tilsvarer 400 MHz. De neste generasjonene av SLDRAM bør operere ved frekvenser på 400 MHz og høyere, det vil si gi en effektiv frekvens på mer enn 800 MHz.

Opptil 8 minnebrikker kan kobles til én kontroller. For å unngå forsinkelser i signaler fra brikker lenger unna kontrolleren, bestemmes tidskarakteristikkene for hver brikke og føres inn i kontrollregisteret når strømmen slås på.

ESDRAM-brikker. Dette er en synkron versjon av EDRAM som bruker de samme teknikkene for å redusere tilgangstiden. En skriveoperasjon, i motsetning til en leseoperasjon, omgår hurtigbufferen, noe som øker ESDRAM-ytelsen når lesing gjenopptas fra en linje som allerede er i hurtigbufferen. Takket være tilstedeværelsen av to banker i brikken, minimeres nedetid på grunn av forberedelse til lese-/skriveoperasjoner. Ulempene med mikrokretsen under vurdering er de samme som for EDRAM - komplikasjonen til kontrolleren, siden den må ta hensyn til muligheten for å forberede seg på å lese en ny kjernelinje inn i hurtigbufferminnet. I tillegg, med en vilkårlig sekvens av adresser, brukes cache-minnet ineffektivt.

CDRAM-brikker. Denne typen RAM ble utviklet av Mitsubishi Corporation, og den kan betraktes som en revidert versjon av ESDRAM, fri for noen av dens ufullkommenheter. Kapasiteten til hurtigbufferminnet og prinsippet om å plassere data i det er endret. Kapasiteten til en enkelt hurtigbufferblokk er redusert til 128 biter, slik at 16-kilobit-hurtigbufferen samtidig kan lagre kopier av 128 minneplasseringer, noe som muliggjør mer effektiv bruk av hurtigbufferminnet. Utskifting av den første minneseksjonen plassert i hurtigbufferen begynner først etter at den siste (128.) blokken er fylt. Adkomstmidlene har også endret seg. Dermed bruker brikken separate adressebusser for den statiske cachen og den dynamiske kjernen. Overføring av data fra den dynamiske kjernen til cache-minnet kombineres med utsendelse av data til bussen, så hyppige, men korte overføringer reduserer ikke ytelsen til IC når du leser store mengder informasjon fra minnet og setter CDRAM på linje med ESDRAM, og når du leser på selektive adresser vinner CDRAM klart. Det skal imidlertid bemerkes at endringene ovenfor førte til enda større kompleksitet for minnekontrolleren.

RAM- Dette er et minneområde som prosessoren samhandler intensivt med mens datamaskinen kjører. Det (etter nedlasting) lagrer aktiv programmer og data som brukes under en enkelt datamaskinøkt. Før du slår av datamaskinen eller før du trykker på Tilbakestill-knappen, må resultatene av arbeidet (mottatte data) lagres på en ikke-flyktig lagringsenhet (for eksempel på en harddisk).

Dette kapittelet er viet det strukturelle-funksjonelle og logisk organisering tilfeldig tilgang minne. Den diskuterer prinsippene for konstruksjon, drift og hovedegenskaper til RAM; strukturen til RAM, dens inndeling i områder og formålet med disse områdene; hovedtyper av RAM-brikker, RAM-moduler, etc.

Minneelementer

Navn "dynamisk RAM" skyldes minneelementer, som er små kondensatorer som er i stand til å lagre ladning, som vist nedenfor. Under reelle forhold er kondensatoren utladet og krever konstant periodisk opplading. Derfor er minne basert på kapasitive elementer dynamisk minne, som er fundamentalt forskjellig fra statisk minne implementert på bistabile celler som er i stand til å lagre informasjon når strømmen er på i uendelig lang tid. Dermed betyr dynamisk datalagring for det første muligheten for gjentatte ganger å skrive informasjon inn i RAM, samt behovet for periodisk (omtrent hver 15. ms) oppdatering, eller omskriving av data.

Ved bruk av kapasitive minneelementer er det mulig å plassere millioner av celler på én brikke og få det billigste halvlederminnet med tilstrekkelig høy ytelse med moderat strømforbruk. Takket være dette er dynamiske RAM-er grunnleggende datamaskinens minne.

Om muligheten for å bruke en kondensator som et minneelement. En ideell kondensator er en to-terminal enhet hvis ladning Q er lineær funksjon Spenning U(Fig. 10.1, EN). Hvis til en ideell kondensator C gjennom en bryter TIL ta med spenning U fra EMF-kilde(Fig. 10.1.6), så vil kondensatoren vises konstant ladning Q i samsvar med volt-coulomb-karakteristikken (fig. 10.1, EN). Med konstant ladning (Q= const) ingen strøm flyter i kretsen (/= AQ/At= 0), derfor vil åpning av nøkkelen (fig. 10.1, c) ikke endre tilstanden til kondensator C, dvs. kondensatoren vil fortsatt ha 0 = const og U= konst. Derfor, Kondensatoren har evnen til å lagre lade Qw spenning U.

Ris. 10.1. Volt-coulomb karakteristisk for en ideell kondensator (a), dens tilstand når den er lukket (b) og åpne (inn) nøkkel TIL, krets for utlading av kondensator C gjennom en motstand R(g)

Ekte kondensatorer har tap i tillegg, for å implementere skrive- og lesemoduser, er eksterne kretser koblet til kondensatorene, som også har tap. Tap er simulert aktiv motstand R, koblet parallelt til kondensator C (fig. 10.1d). Under disse forholdene, når nøkkelen åpnes TIL i kretsen på fig. 10.1.5 gjennom en motstand R strøm / vil begynne å flyte (fig. 10.1, d) og akkumuleres i kondensatoren MED den elektriske feltenergien vil bli omdannet til termisk energi som frigjøres over motstanden R. Under utladingsprosessen mister kondensatoren ladningen og spenningen ved polene synker. Derfor, som nevnt ovenfor, krever bruk av kondensatorer som minneelementer periodisk restaurering (regenerering) Spenning.

På implementeringen av et kapasitivt minneelement. Grunnlaget for å konstruere kapasitive minneelementer er MOSFET-er. For tiden er enkelttransistorstrukturer mye brukt, som i tillegg til det kapasitive minneelementet har et middel for å koble det til bitbussen. Strukturen til et enkelt-transistor minneelement er vist i fig. 10.2a og er en n-MOS transistor der avløpet, laget av polysilisium, ikke har en ekstern terminal. Dreneringen av transistoren danner en plate av kondensatoren, substratet danner den andre. Dielektrikumet mellom platene er et tynt lag av silisiumoksid. Si O 2. Kilde-port-drain-strukturen utfører funksjonene til en transistorbryter. Minneelementdiagrammet er vist i fig. 10.2,6.

Et kapasitivt minneelement med én transistor er enklere enn et statisk RAM-minneelement som inneholder 6 transistorer (fig. 10.2, EN). Fordi flere minneelementer kan plasseres på en brikke, har dynamisk RAM betydelig større minnekapasitet enn sine statiske motstykker.

Ris. 10.2. Struktur minneelement dynamisk RAM(EN) og dens tilsvarende krets (b)

Drift av et minneelement i dynamisk RAM. Bruken av kapasitive minneelementer i minnet påvirker strukturen til stasjonen. I tillegg til minneelementer inneholder stasjonen ytterligere enheter og komponenter som gir de nødvendige betingelsene for normal funksjon. For å vurdere prinsippene for drift av et minneelement i dynamisk RAM, vil vi bruke diagrammet presentert i fig. 10.3, EN. Portene til transistorbryterne til minneelementene er koblet til adressebussene (rader), kildene er koblet til bitbussene (kolonner).

Hvis det ikke er spenning på adressebussen, transistoren UT 1 er låst og kondensatoren SEP til minneelementet kobles fra bitbussen. Minneelementet fungerer i lagringsmodus.

Når spenning påføres adressebussen og derfor til porten til transistorbryteren VT 1 minneelement er koblet til bitbussen. Avhengig av verdien på lese-/skrivesignalet er det mulig to driftsmodus for det kapasitive minneelementet.

I opptaksmodus ved hjelp av kontrollsignaler som leveres til portene til transistorbrytere VT 3 eller VT 4 kan en logisk null eller en skrives til minneelementet, henholdsvis. Hvori logisk null tilsvarer en null spenningsverdi på kondensatoren Sep, en logisk enhet – en spenning lik E.

Ris. 10.3.

I lesemodus, på grunn av den store lengden på bitbussen og stort nummer av forskjellige elementer koblet til den, har bussen en kapasitet CY som er mange ganger større enn kapasiteten Sep til minneelementet. For å lese informasjon fra bitbussen når du kobler et kapasitivt minneelement til den, er det nødvendig å plassere eksakt verdi bussspenning. Derfor, før lesing, påføres en fast spenning lik spenningen til strømforsyningen til bitbussen E eller E/ 2, for å lade opp kapasiteten til Su. Etter dette kobles minneelementet til bitbussen.

Analysen viser at:

- Ved lesing av minneelementet endres spenningen med ±рЕ/ 2, hvor R= sep/telling er en destruktiv prosess og krever restaurering bakgrunnsinformasjon;

- Spenning på bitbussen i lesemodus varierer innenfor ubetydelige grenser, noe som gjør det vanskelig å nøyaktig fange dataene som er lagret i minneelementet.

For å overvinne disse manglene, tas følgende tiltak:

- for å gjenopprette ladningen til minneelementet, introduserer de regenereringssykluser;

- øke kapasiteten SEP av minneelementet, for eksempel ved å bruke et dielektrikum med en høyere dielektrisk konstant;

- redusere kapasiteten C ydischarge buss knapt ganger ved å dele den i to pads;

- For lesing, høysensitive differensialforsterkere med positiv tilbakemelding – forsterkere-regeneratorer.