Организацията на паметта на страницата се използва само в защитен режим, ако в контролния регистър CR0 битът PG = 1.

Основната употреба на превод на адрес на страница е свързана с внедряването виртуална памет, което позволява на програмиста да използва повече пространство в паметта от физическата основна памет.

Принцип виртуална паметпредполага, че потребителят, когато изготвя своята програма, има работа не с физическа RAM, която действително работи като част от компютъра и има някакъв фиксиран капацитет, а с виртуална (привидна) едностепенна памет, чийто капацитет е равен на цялото адресно пространство, определено от размера на компютъра с адресна шина (Lsha):

За 32-битов микропроцесор:

Програмистът има на разположение адресно пространство, ограничено само от ширината на адресната шина, независимо от реален капацитет оперативна паметкомпютър и количеството памет, което се използва от други програми, обработвани паралелно в многопрограмен компютър.

Виртуална памет, предоставяйки на програмиста възможност за достъп до много голям обем от непрекъснато адресно пространство, предоставено на негово изключително разположение, има обичайните свойства: байт-байт адресиране, време за достъп, сравнимо с времето за достъп до RAM.

На всички етапи от подготовката на програмата, включително зареждането в паметта, програмата се представя във виртуални адреси и само когато се изпълни машинна команда, виртуалните адреси се преобразуват във физически. За всяка програма, изпълнявана в многопрограмен режим, се създава собствена виртуална памет. Всяка програма използва едни и същи виртуални адреси от нула до най-големия в дадена архитектура.

За преобразуване на виртуални адреси във физически, физическата и виртуалната памет се разделят на блокове с фиксирана дължина, наречени страници. Обемите на виртуалните и физическите страници са еднакви. Виртуални и физическа паметса номерирани. Страниците, липсващи от физическата памет, обикновено се съхраняват в външна памет. Фиксиран размерна всички страници ви позволява да заредите всяка желана виртуална страница във всяка физическа страница.

Както беше отбелязано по-горе, при странично представяне на паметта виртуалният (логически) адрес е число виртуална страницаи отместването в тази страница. От своя страна физическият адрес е номерът на физическата страница и отместването в нея.

Правилата за преобразуване на номера на виртуални страници във физически номера на страници обикновено се определят под формата на таблица за страниране. Такива таблици се формират от системата за управление на паметта и се променят всеки път, когато паметта се преразпределя. операционна системапостоянно следи състоянието на виртуалните страници на определена програма и определя дали тя е в RAM и ако е така, на кое конкретно място. Приложни програмине се влияят от процеса на страниране и могат да използват цялото адресно пространство. Процесорът автоматично генерира специален случай на неприсъствие, когато програма има достъп до страница, която не е във физическата памет. Когато обработва този специален случай, операционната система зарежда исканата страница от външна памет, като по избор изпраща друга страница на диска (процес на размяна).

Преводът на виртуални адреси във физически е илюстриран на фиг. 3.12.

Ориз. 3.12.Принципът на преобразуване на адрес на виртуална страница във физически

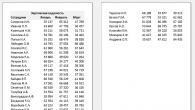

Нека да разгледаме пример за преобразуване на адрес на виртуална страница във физически адрес на страница. Нека компютърът използва адресно пространство за пейджинг от V страница = 1I и има RAM V RAM = 3 страници. Нека четири програми се изпълняват едновременно на компютър със следния брой страници: V A = 2, V B = 1, V C = 3, V D = 2. Превключването между програмите става чрез квантово време t k = 1. Времето за изпълнение на всяка страница на всяка програма е t = 2t k. Вярваме, че програмните страници се зареждат в RAM при необходимост и когато е възможно. свободни площи RAM. Ако цялата памет е заета, тогава нова страницазамества този, който не е бил достъпван най-дълго време.

При такива условия таблицата за натоварване на RAM и таблиците за преобразуване на страници за всяка програма ще имат формата, представена в табл. 3.2.

В таблицата за разпределение на RAM броят страници, активни в даден цикъл, е подчертан. В таблиците за преобразуване на страници тиретата показват ситуации, когато дадена виртуална страница не е в RAM.

| Таблица 3.2. Пример за разпределение на паметта на страницата в многопрограмен компютър | |||||||||||||||||

| Страница | Така че вие | ||||||||||||||||

| Динамично разпределение на паметта | |||||||||||||||||

| RAM 0 | АД | АД | АД | НАПРАВЕТЕ | НАПРАВЕТЕ | НАПРАВЕТЕ | CO | CO | CO | C1 | C1 | C1 | C1 | C1 | C1 | C1 | |

| B0 | B0 | B0 | A0 | A0 | A0 | D0 | D0 | D0 | D1 | D1 | D1 | D1 | D1 | D1 | |||

| C0 | C0 | C0 | B0 | B0 | B0 | A1 | A1 | A1 | A1 | A1 | A1 | C2 | C2 | ||||

| Таблица за страници за програма А | |||||||||||||||||

| А 0 | - | - | - | - | - | - | - | - | - | - | - | ||||||

| - | - | - | - | - | - | - | - | - | - | ||||||||

| Таблица за страници за програма B | |||||||||||||||||

| B 0 | - | - | - | - | - | - | - | - | - | - | |||||||

| Таблица за страници за програма C | |||||||||||||||||

| От 0 | - | - | - | - | - | - | - | - | - | - | |||||||

| - | - | - | - | - | - | - | - | - | |||||||||

| - | - | - | - | - | - | - | - | - | - | - | - | - | - | ||||

| Таблица за страници за програма D | |||||||||||||||||

| D0 | - | - | - | - | - | - | - | - | - | - | |||||||

| - | - | - | - | - | - | - | - | - | - |

Ако всяка страница има обем от 1000 адресируеми клетки, тогава, например, в цикъл 9, достъп до виртуален адрес 1100 на програма A (виртуална страница 1, отместването на страницата е 100) ще доведе до извикване на физически адрес 2100 (физическа страница 2, отместването на физическа страница е същото като виртуалното, т.е. 100).

Нека сега разгледаме приложението им основни принципипреобразуване на адрес на страница в микропроцесор с архитектура IA-32 с размер на страницата 4 KB.

Базата за пейджинг е 32-битова линеен адрес, получени на етапа на трансформация на сегмента логичен адрес. Пейджинг се извършва, когато битът PG е настроен на 1 в контролния регистър CR0.

В този случай най-високите 20 бита линеен адресвсъщност представлява номера на виртуалната страница. Въпреки това, директно преобразуване в една стъпка на това число във физически номер на страница изисква таблица от 2 20 елемента, всеки с дължина 4 байта (20-битов номер на страница плюс някои Допълнителна информация), т.е. 4 MB. В мултипрограмна среда такава таблица може да се изисква за всяка задача. Тази таблица трябва да се съхранява постоянно в RAM, за да не се увеличи значително времето, необходимо за генериране на физически адрес. За тези цели ще е необходимо постоянно да се резервира значителна част от капацитета на RAM, което беше практически невъзможно на етапа на появата на първите MP-базирани компютри с архитектура IA-32.

Вместо това микропроцесорът използва двустепенно пейджинг на адреси. Основната страница, наречена директория с таблици на страници(KTS), съдържа 1024 32-битови таблица на страници елемент директория(ECTS - PDE запис в директорията на страницата). Всеки от тях се обръща към подчинен таблица на страниците(TS), т.е. разрешени са общо до 1024 таблици на подчинени страници. Всяка таблица на страници съдържа 1024 32-битови елемент на таблицата на страницата(ETS - PTE запис в таблицата на страниците), всеки от които адресира физическа страница. Така общият брой адресируеми физически страници е 2 20, т.е. цялото виртуално адресно пространство (4 KB * 220 елемента = 2 32 байта). Всяка таблица заема 1024 4 = 4 KB, тоест точно 1 страница. Общият размер на таблиците, използвани за страниране, не е намалял, а дори леко се е увеличил поради използването на каталога на таблиците на страниците. Въпреки това, първо, почти винаги в една система този размер може да бъде значително намален поради факта, че някои линейни адресиникога няма да се формира (и тази информация е дадена дескрипторни таблицисегменти) и не е необходимо да създавате таблица на страници за тях. И второ, само таблица на страници директория и таблица на странициизпълнявана в момента програма. Почивка таблици на страницитеможе временно да се съхранява във външна памет.

Ориз. 3.13.Преобразуване на линейна във физическа адресна страница

Така преобразуването на линеен адрес във физически има формата, показана на фиг. 3.13.

Горните 20 цифри линеен адрессе разделят на две 10-битови полета: поле таблица на страници номера на каталожни позициии поле номера на елементите на таблицата на страниците. От директория с таблици на страници, и всеки таблица на страницитезаемат точно 1 страница и са подравнени към границата на страницата, тогава долните 12 бита от основния им адрес са нула и 20-битово поле е достатъчно, за да се определи физическият им адрес.

За директория с таблици на страницинеговият 20-битов адрес е в контролния регистър CR3. CTS е постоянно в паметта и не участва в размяната.

Горните 20 бита на физическия адрес таблици на страницитеса извлечени от СТЕ. Структурите на елемента CTS и елемента TS са подобни (фиг. 3.14).

Ориз. 3.14.Структура на каталожни елементи на таблица на страници и таблици на страници

Най-високите 20 бита на елемента дават базов адрес таблици на страниците(в ECTS) или физическа страница (в ETS). Битовете P, A, R/W и U/S имат определени прилики с тези на сегментния дескриптор; други битове имат специфични цели.

Бит за присъствие P показва дали адресът на рамка на страница (таблица на страници или страница с памет) е картографиран към страница във физическата памет. Когато P = 1, страницата присъства в RAM. Когато P = 0, няма страница в паметта и достъпът до тази страница причинява прекъсване на грешка на страницата.

Бит за достъп A се настройва от микропроцесора в състояние A = 1 при достъп до тази рамка на страницата за писане или четене на информация.

Бит за модификация D (Dirty - “мръсен”) се задава от процесора равно на 1 в елемента ETS при запис на тази страница. За записи в директория на таблица на страници стойността на бита D е недефинирана. При зареждане на страница в паметта операционната система нулира бит D. Ако, когато е необходимо да разтоварите страница във външна памет, се окаже, че D = 0 за нея, това означава, че не е имало достъп за запис на страницата в памет; има нейно точно копие във външната памет и няма нужда действително да прехвърляте страницата от паметта на диска. Това спестява време при смяна.

Битът за четене-запис R/W и битът U/S (потребител/супервизор) определят правата за достъп до таблицата на страниците или страницата за програми с различни нива на привилегии. Има само 2 нива на привилегии за страниците: ниво на надзорник (U/S = 0), съответстваща на стойността DPL на сегмент 0, 1, 2 и потребителско ниво (U/S = 1), съответстващо на DPL = 3. Ако се направи заявка към страницата с ниво на привилегия 3 (потребителски програми), тогава със стойност U/S = 0 е отказан достъп до съответната таблица или страница. Ако U/S = 1, тогава, когато R/W = 0, е разрешено само четене на таблицата или страницата, а когато R/W = 1, са разрешени както четенето, така и писането.

За заявки с високи привилегии (система програмни нива 0, 1, 2) писането и четенето на таблици и страници е разрешено за всякакви стойности на U/S, R/W (Таблица 3.3).

Битовете PWT и PCD се използват за управление на работата на кеш паметта по време на адресиране на страници. PCD бит - забранете кеширането на страници. Когато PCD = 1, кеширането е деактивирано. Битът PWT е битът за обратно записване на страницата. Определя метода за актуализиране на външния кеш (L2 кеш). Когато PWT = 1, актуализацията се извършва чрез метода на запис (както за вътрешния кеш), когато PWT = 0, чрез метода на обратно записване.

Битове 9...11 в ECTS и ETS са запазени за операционната система. Процесорът никога не използва или модифицира тези битове. Разработчиците на ОС могат да използват тези битове, за да съхраняват информация за стареенето на страницата, да определят кои страници трябва да бъдат заменени от външна памет и за други цели.

Старши 10 цифри линеен адресзаедно със съдържанието на контролния регистър CR3 определят необходимите таблица на страници елемент директория. Следващите 10 бита от линейния адрес съдържат номера на запис в избраната таблица на страниците.

Тъй като и ECTS, и ETS са дълги 4 байта, за да се получи отместването на началото на даден елемент спрямо началото на съответната таблица, неговият номер трябва да се умножи по 4.

Последните 12 цифри линеен адрессъдържат отместване в страницата. По този начин сумата от отместването на страницата и основния адрес на страницата, извлечени от ETS, дава физическия адрес на търсения байт.

Има две други схеми за организиране на виртуална памет:

· сегментен;

· сегментна страница.

Идеите за сегментиране са очертани във въведението към Раздел 10. При сегментна организация виртуалният адрес все още е двуизмерен и се състои от две полета - номера на сегмента и отместването в рамките на сегмента. Имайте предвид, че от гледна точка на ОС сегментите са логически единици и основната им цел е да съхраняват и защитават хомогенна информация (код, данни и т.н.).

От гледна точка на потребителя процесът обикновено се представя не като линеен масив от байтове, а като набор от сегменти с променлив размер (данни, код, стек). Сегментирането е схема за управление на паметта, която поддържа този потребителски изглед. Сегментите съдържат процедури, масиви, стекове или скалари, но обикновено не съдържат информация от смесен тип.

Програмисти, които пишат на езици ниско нивотрябва да има представа за организацията на сегмента, като изрично променя стойностите на сегментните регистри (това е ясно видимо в текстовете на програмите, написани на асемблерен език). Логическото адресно пространство е набор от сегменти. Всеки сегмент има име, размер и други параметри (ниво на привилегии, разрешени типове повиквания, флагове за присъствие). Потребителят определя всеки адрес с две стойности: името на сегмента и отместването. (За разлика от схемата за пейджинг, при която потребителят посочва само един адрес, който се разделя от хардуера на номер на страница и отместване по прозрачен за програмиста начин.)

Всеки сегмент е линейна последователност от адреси от 0 до максимум. Различните сегменти могат да имат различни дължини, които могат да се променят динамично (например стеков сегмент). В елемент на сегментна таблица, в допълнение към физическия адрес на началото на сегмента (ако виртуален сегментсъдържащ се в основната памет) съдържа дължината на сегмента. Ако размерът на отместването във виртуалния адрес надвишава размера на сегмента, възниква прекъсване.

Логически адрес - подредена двойка v=(s,d), номер на сегмент и отместване в сегмента.

В системи, където сегментите се поддържат в хардуера, тези параметри обикновено се съхраняват в таблица дескрипторисегменти и програмата препраща към тези дескриптори чрез числа селектори. Освен това контекстът на всеки процес включва набор сегментни регистри, съдържащ селектори на текущите кодови сегменти, стек, данни и т.н. и дефиниращи кои сегменти ще се използват, когато различни видоведостъпи до паметта. Това позволява на процесора да определя на хардуерно ниво допустимостта на достъп до паметта, опростявайки прилагането на защита на информацията от повреда и неоторизиран достъп.

Ориз. 11.2 Преобразуване на логически адрес със сегментирана организация на паметта.

Хардуерната поддръжка за сегменти е сравнително слаба (основно на процесори Архитектура на Intel) и се характеризира доста бавно зарежданеселектори в сегментни регистри, изпълнявани при всяко контекстно превключване и всеки преход между различни сегменти. В системи с чисто странична организация на паметта, за да се опише типичното адресно пространство на процес, което е набор от сегменти, сегментирането се изпълнява на ниво, независимо от хардуера.

Съхраняването на големи сегменти в паметта може да бъде неудобно. Възниква идеята да ги пейджинг. При сегментна страница За да се организира виртуалната памет, се извършва превод на две нива на виртуален адрес във физически. В този случай виртуалният адрес се състои от три полета: номера на сегмента на виртуалната памет, номера на страницата в сегмента и отместването в страницата. Съответно се използват две таблици за съпоставяне - таблица на сегменти, свързваща номера на сегмента с таблицата на страниците, и отделна таблица на страници за всеки сегмент.

Ориз. 11.3 Формиране на физически адрес със сегмент- организация на страницатапамет.

Организацията на сегментна страница на виртуалната памет направи възможно споделянето на едни и същи сегменти от данни и програмен кодвъв виртуална памет различни задачи(всяка виртуална памет имаше отделна сегментна таблица, но споделените таблици на страници се поддържаха за споделени сегменти).

Асоциативна памет.

Намирането на желаната страница в таблица със страници на много нива, което изисква няколко достъпа до основната памет по пътя за преобразуване на виртуален адрес във физически, отнема много време. При някои обстоятелства такова забавяне е неприемливо. Този проблем намира решение и на ниво компютърна архитектура.

Поради свойството локалност, повечето програми препращат към малък брой страници за определен период от време, така че само малка част от таблицата на страниците работи усилено.

Естественото решение е да оборудвате компютъра с хардуерно устройство за картографиране на виртуални страници към физически страници без достъп до таблицата на страниците, тоест да имате малка, бърза кеш памет, която съхранява необходимите този моментчаст от таблицата на страниците. Това устройство се нарича асоциативна памет, понякога те също използват термина асоциативни регистри (понякога буфер за преглед на превода (TLB)).

Един запис в таблицата на асоциативна паметсъдържа информация за една виртуална страница, нейните атрибути и рамката, в която се намира. Тези полета съответстват точно на полетата в таблицата на страниците.

Картографирането на виртуални страници, съхранени в асоциативна памет, е бързо, но кеш паметта е скъпа и има ограничен размер. Броят на записите в TLB е от 8 до 2048.

Паметта се нарича асоциативна, защото за разлика от таблицата на страниците, която се индексира с номера на виртуални страници, тук номерът на виртуалната страница се сравнява едновременно със съответното поле във всички редове на тази малка таблица. Следователно тази памет е скъпа. Редът, чието поле за виртуална страница отговаря на желаната стойност, съдържа номера на рамката на страницата.

Нека разгледаме функционирането на мениджъра на паметта при наличие на асоциативна памет. Първо търси виртуална страница в асоциативната памет. Ако страницата бъде намерена, всичко е наред, освен в случаите на нарушаване на привилегиите, когато заявката за памет се отхвърля.

Ако дадена страница не е в асоциативната памет, тя се търси в таблицата на страниците. Една от страниците в асоциативната памет се заменя с намерената страница. В таблицата така заредената страница се маркира с модифициращ бит, който ще бъде отчетен при следващото зареждане на асоциативната памет от таблицата на страниците.

Процентът пъти, когато номер на страница е в асоциативната памет, се нарича коефициент на попадение. По този начин коефициентът на попадение е частта от връзките, които могат да бъдат направени с помощта на асоциативна памет. Достъпът до едни и същи страници увеличава коефициента на попадение.

Да предположим например, че са необходими 100 ns за достъп до таблицата на страниците и 20 ns за достъп до асоциативната памет. При коефициент на попадение от 90%, средното време за достъп е 0,9*20+0,1*100 = 28 ns.

Доста приемливата производителност на съвременните операционни системи доказва ефективността на използването на асоциативна памет. Висока стойноствероятността данните да бъдат открити в асоциативната памет е свързана с наличието на обективни свойства на данните: пространствена и времева локалност.

Необходимо е да се обърне внимание на следния факт. Когато превключвате процеси, трябва да се уверите, че нов процесне видя в асоциативната памет информация, свързана с предишния процес, например, за да го изчисти. Че. използването на асоциативна памет увеличава времето за превключване на контекста.

Йерархия на паметта.

Всички предишни аргументи са валидни и за други двойки устройства за съхранение, например за RAM и външна памет. В този случай средното време за достъп до данните, разположени на диска, се намалява, а ролята на кеш памет се играе от буфер в RAM.

Разгледаната от нас тристепенна схема на паметта (асоциативна, първична, вторична) е специален случай многостепенна памет.Например, както е показано на фиг. 11.5, типовете памет могат да бъдат организирани в йерархия в низходящ ред на скоростта на достъп и нарастващата цена.

.

Ориз. 11.5 Йерархия на компютърната памет

Смята се, че разходите, свързани с копирането на информация от една памет в друга, ще бъдат по-малки от печалбата в производителността, която се получава чрез намаляване на времето за извличане от по-бързи слоеве памет. Информация за страницата, която е в паметта Най-високо ниво, също се съхранява на нива с големи числа. Ако процесорът не намери правилната страница на i-то ниво, той започва да я търси на следващите нива. Кога желаната страницаоткрит, той се прехвърля на по-бързи нива. В този случай се получава някакво изместване стара страница, обикновено този, който не е използван най-дълго. Идеята е да се гарантира, че страниците, които са най-необходими в момента, са в по-бързите части на паметта. Ефективността на такава схема се дължи на същото свойство локалност (повече подробности относно локалността и свързаната концепция за работен набор от страници ще бъдат обсъдени в следващата глава). В резултат на това средното време за достъп за схема на многостепенна памет се оказва много близко до времето за достъп на първо ниво.

Размер на страницата

Дизайнери на ОС за съществуващи машинирядко имат способността да влияят върху размера на страницата. Въпреки това, за отново създават се компютрирешение относно оптимален размерстраницата е актуална. Както може да очаквате, няма нито един най-добър размер. По-скоро има набор от фактори, които влияят на размера. Обикновено размерът на страницата е степен на две от 2**9 до 2**14 байта.

как по-голям размерстраници, толкова по-малък ще бъде размерът на структурите от данни, обслужващи преобразуването на адреси, но толкова по-големи ще бъдат загубите, свързани с факта, че паметта може да се разпределя само страница по страница.

Как да избера размера на страницата? Първо, трябва да вземете предвид размера на таблицата на страниците, тук е препоръчително голям размерстраници (има по-малко страници, следователно таблицата със страници е по-малка). От друга страна, паметта се използва по-добре с малък размер на страницата. Средно половината последна страницапроцесът изчезва. Трябва също така да имате предвид количеството I/O за интерфейс с външна памет и други фактори. Проблемът няма добър отговор. Историческата тенденция е да се увеличава размерът на страницата. По правило размерът на страницата се задава от хардуера, например на Intel е 4096 байта (или 4 KB), на DEC PDP-11 - 8 KB, на DEC VAX - 512 байта, на други архитектури като Motorola 68030, размерът на страницата може да бъде зададен програмно.

И така, хардуерните характеристики на поддръжката на виртуална памет са разгледани. Нека да преминем към неговата софтуерна поддръжка.

Странична организация на виртуалната памет

В повечето съвременни операционни системи виртуалната памет е организирана чрез адресиране на страници. RAM е разделена на страници: области на паметта с фиксирана дължина (например 4096 байта), които са минимална единицаразпределена памет (тоест дори заявка за 1 байт от приложението ще доведе до разпределяне на страница памет към него). Процесът осъществява достъп до паметта, използвайки адрес на виртуална памет, който съдържа номера на страницата и отместването в страницата. Процесорът преобразува номера на виртуалната страница в адреса на съответната физическа страница, използвайки буфер за асоциативен превод. Ако той не успее да направи това, тогава е необходим достъп до таблицата на страниците (т.нар. Page Walk), който може да бъде осъществен както от самия процесор, така и от операционната система (в зависимост от архитектурата).

(слайд № 12)

Ориз. 16.4.Пример за организация на страница.

Организация на страницата (страниране) –стратегия за управление на паметта, в която:

Логическата памет се разделя на страници– съседни области с еднаква дължина, обикновено степен 2 (например 512 думи);

физическата памет съответно се разделя на рамкисъщия размер;

разпространение логическа паметслучва се с точност на страницата;

· физическата памет на даден процес може да не е непрекъсната;

Връзката между логическата и физическата памет на процеса се осъществява с помощта на таблици на страниците– структура на системата, разпределени на процеса за излъчваниянеговият логически адреси към физически.

С организацията на страницата ОС съхранява информация за всички свободни рамки. Тъй като паметта се разпределя на база страница по страница, е възможно вътрешно фрагментиране.

Целите на пейджинг са да позволи на процесите да разпределят физическата памет несвързано и да разширят пространството на логическата памет.

На ориз. 16.4Даден е пример за организация на страницата, който показва, че за разлика от непрекъснатата логическа памет на процес, съответните рамки на страници в основната памет може да не са разположени непрекъснато: логическа страница 0 съответства на рамка 1, страница 1 на рамка 4, страница 2 до кадър 3, страница 3 – кадър 7.

(слайд № 13)

Ориз. 16.5.Пример за организация на страницата в блокове от по 4 страници.

На ориз. 16.5даден е друг възможен пример за организация на страницата: логическата и физическата памет са разделени на блокове от по 4 страници в един ред; Таблицата на страниците не съхранява номера на страницата, а номера на блока на страницата. Например елемент 0 на таблицата на страниците съхранява блок номер 5, при който адресът на началото на блока се изчислява чрез умножаване на съдържанието на елемента на таблицата на страниците по размера на блока, равен на 4 (резултат - 20).

Реализация на таблица на страници

Използване на асоциативна памет.Таблицата със страници е непрекъсната област от физическата памет. Системата има базов регистър на таблицата на страниците (PTBR),сочещи към таблицата на страниците и запаметяващи нейната дължина.

По този начин, с организация на страници, всеки достъп до паметта всъщност изисква не един, а два достъпа до паметта - единият към таблицата на страницата, другият директно към данните или командата. Това е известен недостатък и неефективност на организацията на страницата в сравнение с други прости методиуправление на паметта.

(слайд № 14)

Ориз. 16.3.Архитектура на превод на адреси за пейджинг.

При страницата организация логическият адрес се обработва от системата по специален начин - като структура (p, d):най-високите му цифри означават номер на страницата, юноши – отместване в рамките на страницата. Номер на страница (p)се третира като индекс в таблицата на страниците, чийто съответен елемент съдържа основата адрес на началото на страницата във физическата памет. Отместване в рамките на страница (d)се добавя към неговия основен адрес. Резултатът е физически адрес, който се предава на устройството за управление на паметта. Архитектурата на превод на адреси за пейджинг е показана в ориз. 16.3.

(слайд № 15)

Ориз. 16.7.Схема за превод на адреси, използваща асоциативна памет.

Проблемът с две повиквания се решава чрез въвеждане асоциативна памет (кеш) на страници,също наричан буфер за превод (TLB).Асоциативната памет е по същество асоциативен списък от двойки от формата: (номер на страница, номер на рамка).Производителността му е значително по-висока от тази на основната памет и регистрите.

Схемата за превод на адреси, използваща асоциативна памет, се променя: ако номер на страницатаот логическия адрес се намира в асоциативната памет, след което съответният елемент се извлича от неговия елемент номер на рамката.Ако номерът на страницата не е в асоциативната памет, той се избира по обичайния начинот таблицата на страниците, но се съхранява в асоциативна памет. Така в асоциативната памет се натрупва информация за най-често използваните страници.

Илюстрирана е модифицирана схема за преобразуване на адреси, използваща TLB ориз. 16.7.

В странираните системи основната и външната памет (главно дисково пространство) са разделени на блокове или страници с фиксирана дължина. На всеки потребител се предоставя определена част от адресното пространство, която може да надвишава основната памет на компютъра и която е ограничена само от възможностите за адресиране, присъщи на системата с инструкции. Тази част от адресното пространство се нарича потребителска виртуална памет. Всяка дума във виртуалната памет на потребителя се определя от виртуален адрес, състоящ се от две части: битовете от висок ред на адреса се считат за номер на страница, а битовете от нисък ред се считат за номер на думата (или байт) вътре в страницата.

Различните нива на памет се управляват от програми на ядрото на операционната система, които наблюдават разпределението на страниците и оптимизират обмена между тези нива. При пейджинг на паметта не е необходимо последователните виртуални страници да се намират на последователни страници на основната физическа памет. За да посочи съпоставянето между виртуални страници и страници от основната памет, операционната система трябва да генерира таблица със страници за всяка програма и да я постави в основната памет на машината. В този случай всяка страница от програмата, независимо дали е в основната памет или не, е свързана с някакъв елемент от таблицата на страниците. Всеки елемент от таблицата на страниците съдържа номер на физическа страница в основната памет и специален индикатор. Едно състояние на този индикатор показва наличието на тази страница в основната памет. Нулевото състояние на индикатора означава, че няма страница в RAM.

За да повишат ефективността на този тип схеми, процесорите използват специална, напълно асоциативна кеш памет, която също се нарича транслационен буфер (TLB). Въпреки че наличието на TLB не променя принципа на дизайна на страниците, от гледна точка на защитата на паметта е необходимо да се осигури възможност за изчистването му при превключване от една програма към друга.

Търсенето в таблиците на страниците, намиращи се в основната памет, и зареждането на TLB може да се извърши и от двете програмно, или специален хардуер. В последния случай, за да се предотврати възможността за регрес потребителска програмаТаблиците на страниците, към които не е свързан, са обект на специални мерки. За тази цел процесорът осигурява допълнителен защитен регистър, съдържащ дескриптор на таблица на страници или двойка основа-граница. Базата определя адреса на началото на таблицата на страниците в основната памет, а границата определя дължината на таблицата на страниците на съответната програма. Зареждането на този регистър за сигурност е разрешено само в привилегирован режим. За всяка програма операционната система съхранява манипулатор на таблицата на страниците и го задава в регистъра за сигурност на процесора, преди да стартира съответната програма.

Нека отбележим някои присъщи характеристики прости веригис организация на паметта на страницата. Най-важното от тях е, че всички програми, които трябва да комуникират директно една с друга без намеса на операционната система, трябва да използват общо виртуално адресно пространство. Това важи и за самата операционна система, която най-общо казано трябва да работи в режим на динамично разпределение на паметта. Следователно в някои системи виртуалното адресно пространство на потребителя е съкратено от размера на общите процедури, до които потребителските програми искат да имат достъп. Общи процедуриОпределено количество виртуално адресно пространство трябва да бъде разпределено за всички потребители, така че те да имат постоянно място в таблиците на страниците на всички потребители. В този случай, за да се гарантира целостта, трябва да се осигури секретност и взаимна изолация на изпълняващите се програми различни режимидостъп до страници, които се реализират с помощта на специални индикатори за достъп в елементите на таблицата на страницата.

Резултатът от тази употреба е значително увеличение на таблиците на страниците на всеки потребител. Едно решение на проблема с намаляването на дължината на таблиците се основава на въвеждането на многостепенна организация на таблиците. Специален случай на многостепенна организация на таблици е сегментирането с организация на паметта на страниците. Необходимостта от увеличаване на потребителското адресно пространство се обяснява с желанието да се избегне необходимостта от преместване на части от програми и данни в адресното пространство, което обикновено води до проблеми с преименуването и сериозни трудности при разделянето Главна информациямежду много задачи.

Край на работата -

Тази тема принадлежи към раздела:

Принципи на работа на компютъра. Учебник за курсовете “Технология на програмирането” и “Операционни системи”

Наръчникът очертава основни принципиорганизация и функциониране на компютър, състав на минимален компютър с автобусна организация, предназначение и.. библиограф име..

Ако се нуждаеш допълнителен материалпо тази тема или не сте намерили това, което търсите, препоръчваме да използвате търсенето в нашата база данни с произведения:

Какво ще правим с получения материал:

Ако този материал е бил полезен за вас, можете да го запазите на страницата си в социалните мрежи:

| Tweet |

Всички теми в този раздел:

Принципи на фон Нойман

Мнозинство модерни компютриса изградени на базата на принципи, формулирани от американския учен, един от „бащите” на кибернетиката Й. фон Нойман. Тези принципи са публикувани за първи път от фон Нойман през 19г

Състав и работа на минимален компютър с шинна организация

Автобусната организация е най-простата формакомпютърни организации. Такъв компютър съдържа следните функционални блокове (виж фиг. 1). Контролно устройство (CU) -

Компютърни команди

IN този разделРъководството ще разгледа накратко набора от команди, използвани в типичните компютри, и действията, изпълнявани от тези команди.

Първата от командите (сравнение), както е отбелязано по-горе, изважда стойността на операнд B от операнд A. Ако A>B, тогава резултатът ще бъде положителен и съответно флагът на знака в регистъра на флага

Системни интерфейси с изолирани и общи шинни системи

В предишните раздели, когато описваме обобщения алгоритъм на работа централен процесорумишлено пропуснахме от разглеждане въпроса как процесорът „разграничава“ портовете на външните устройства от клетките

Методи за обмен на данни в машини с шинна организация. Механизъм за прекъсване

След като разгледахме алгоритъма за функциониране на процесора и методите за организиране на шинната система в компютъра, ще се опитаме да разберем какви характеристики въвежда необходимостта от осигуряване на взаимодействие в работата и организацията на компютъра.

Софтуерно контролиран обмен на данни

Тъй като скоростта на работа периферно оборудванеобикновено под скоростта на процесора, за да извърши операция по обмен, процесорът трябва да гарантира, че устройството е готово да извърши операцията

Прекъсване на обмена

За да разберем какво е прекъсване, нека да разгледаме следния пример. Някакъв мъж седи на стол и чете книга. По това време нещо се готви на кухненската печка, а освен това и тя

Директен достъп до паметта извън процесора

Комуникация с бавно движещи се периферни устройства, например, с принтер за символ по знак, е организиран около прекъсвания, които инициират прехвърлянето на всяка дума или байт. Ако подпрограмата

И още за прекъсванията

Описаният по-горе механизъм за прекъсване или хардуерни прекъсвания е ефективен начинорганизиране на взаимодействието на процесора с бавните външни устройстваи започна

Режими на адресиране

Когато изпълнявате програма, много команди изискват достъп до паметта за извличане на данни и запис на междинни и крайни резултати от изчисленията. За всяко такова лечение, както вече беше отбелязано в

Йерархична организация на паметта

Памет в модерни компютрисе изгражда съгл йерархичен принцип. Едно от явленията, характерни за компютрите на фон Нойман, е принципът на локалността. Това означава, че в рамките на ограничен период

Кеш-памет

Както бе споменато по-горе, целта на кеш паметта е временно да съхранява данни и инструкции, често използвани от процесора. Основната структурна единица на кеш паметта е така наречената кеш линия (ок

Сегментна организация на виртуалната памет

Друг подход към организацията на паметта разчита на факта, че програмите обикновено са разделени на отделни сегментни области. Всеки сегмент представлява отделна логическа единица информация,

Процес на пренасочване на виртуална памет

Ще опишем процеса на пренасочване, използвайки примера на микропроцесора 80386 от Intel. Процесът на пренасочване е показан на фиг. 19 и 20. Преди изпълнение моделите на ботушите се поставят в операционната

Формати на данни

Основните типове данни, които се срещат при обработката на информация в компютър, са числа, представени в двоична системачисла, както и буквено-цифрови знаци. Някои компютри също

Компютърен информационен модел

Обработка на числа, символна информация, логическа обработка, обработката на сигнали е в специални случаи обща концепциянад заглавието "обработка на информация". Компютърът се характеризира с: информация

Най-простият конвейер, конвейерно изпълнение

Има доста просто добре известно правило - за да завършите някаква работа по-бързо, трябва да я разделите между няколко изпълнители и да ги принудите да действат едновременно. Веднъж

Структурни конфликти

Структурни конфликти възникват, ако различни части на тръбопровода имат достъп до един, недублиращ се ресурс. Подобна ситуациявъзниква, например, ако процесорът има единичен

Конфликти на данни

Конфликтите на данни възникват, когато няколко последователно изпълнени команди се окажат логически зависими една от друга. Ако редът на достъп до данните по време на обработката на конвейера е сигурен

Намаляване на загубите при изпълнение на команди за преход и минимизиране на конфликтите при управление

Контролните конфликти могат да причинят дори по-големи загуби на производителност на тръбопровода, отколкото конфликтите на данни. Когато се изпълни инструкция за условно разклоняване, тя може да се промени или да не се промени

Компютър с канална организация

Този тип компютърна организация се основава на множеството комуникационни канали между устройствата и функционалната специализация на възлите. Опростена диаграма на организацията на компютър с канали е показана на фиг.

Програмистът има на разположение адресно пространство, ограничен само от битовия капацитет на адресната шина, независимо от действителния капацитет на RAM на компютъра и количеството памет, което се използва от други програми, обработвани паралелно в мултипрограмен компютър.

Виртуална памет, предоставящ възможност на програмиста за достъп до много голям обем от непрекъснато адресно пространство, предоставено на негово изключително разположение, има обичайните свойства: байтово адресиране, време за достъп, сравнимо с времето за достъп до RAM.

На всички етапи от подготовката на програмата, включително зареждането в памет, програмасе появява в виртуални адреси, и то само при изпълнение на машинна команда виртуални адресисе превръщат във физически. За всяка програма, изпълнявана в многопрограмен режим, своя собствена виртуална памет. Всяка програма използва същото виртуални адресиот нула до най-големия в дадена архитектура.

За преобразуване на виртуални адреси във физически физически и виртуална паметса разделени на блокове с фиксирана дължина, наречени страници. Обемите на виртуалните и физическите страници са еднакви. Страниците с виртуална и физическа памет са номерирани. Страниците, липсващи във физическата памет, обикновено се съхраняват във външна памет. Фиксираният размер на всички страници ви позволява да заредите всяка желана виртуална страница във всяка физическа страница.

Както беше отбелязано по-горе, с представяне на странирана памет, виртуалната ( логически) адреспредставлява числото виртуална страницаи отместването в тази страница. На свой ред, физически адрес- този номер физическа страницаи денивелацията в него.

Правила за преобразуване на номера на виртуални страници в числа физически странициобикновено се дава под формата на таблица преобразуване на страници. Такива таблици се формират от системата за управление на паметта и се променят всеки път, когато паметта се преразпределя. операционна системапостоянно следи състоянието на виртуалните страници на определена програма и определя дали тя е в RAM и ако е така, на кое конкретно място. Приложните програми не засягат процеса и могат да се използват от всеки адресно пространство. Процесорът автоматично генерира специален случай на неприсъствие, когато програма има достъп до страница, която не е във физическата памет. Когато обработва този специален случай, операционната система зарежда исканата страница от външна памет, като по избор изпраща друга страница на диска (процес на размяна).

Преводът на виртуални адреси във физически е илюстриран на фиг. 3.12.

Ориз. 3.12.

Нека разгледаме пример за превод на адрес виртуална страницада се физическа страница. Оставете компютъра да използва адресно пространство, което включва страниране с обем V страници = 1I и има RAM V RAM = 3 страници. Нека четири програми се изпълняват едновременно на компютър със следния брой страници: V A = 2, V B = 1, V C = 3, V D = 2. Превключването между програмите става след квантово време t k = 1. преднинавсяка страница от всяка програма е t = 2t k . Ние вярваме, че програмните страници се зареждат в RAM при необходимост и, ако е възможно, в свободните области на RAM. Ако цялата памет е заета, тогава нова страница замества тази, която не е била достъпвана най-дълго време.

При такива условия RAM зарежда таблица и таблици преобразуване на странициза всяка програма ще има формата, представена в табл. 3.2.

В таблицата за разпределение на RAM броят страници, активни в даден цикъл, е подчертан. В таблици преобразуване на странициТиретата показват ситуации, при които това виртуална страницалипсва от RAM.

| Страница | Така че вие | |||||||||||||||

| 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 | 16 | |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Динамично разпределение на паметта | ||||||||||||||||

| RAM 0 | АД | АД | АД | НАПРАВЕТЕ | НАПРАВЕТЕ | НАПРАВЕТЕ | CO | CO | CO | C1 | C1 | C1 | C1 | C1 | C1 | C1 |

| 1 | B0 | B0 | B0 | A0 | A0 | A0 | D0 | D0 | D0 | D1 | D1 | D1 | D1 | D1 | D1 | |

| 2 | C0 | C0 | C0 | B0 | B0 | B0 | A1 | A1 | A1 | A1 | A1 | A1 | C2 | C2 | ||

| Таблица преобразуване на странициза програма А | ||||||||||||||||

| А 0 | 0 | 0 | - | - | 1 | 1 | 1 | - | - | - | - | - | - | - | - | - |

| 1 | - | - | - | - | - | - | - | - | 2 | 2 | 2 | 2 | 2 | 2 | - | - |

| Таблица преобразуване на странициза програма Б | ||||||||||||||||

| B 0 | - | 1 | 1 | 1 | - | 2 | 2 | 2 | - | - | - | - | - | - | - | - |

| Таблица преобразуване на странициза програма С | ||||||||||||||||

| От 0 | - | - | 2 | 2 | 2 | - | 0 | 0 | 0 | - | - | - | - | - | - | - |

| 1 | - | - | - | - | - | - | - | - | - | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 2 | - | - | - | - | - | - | - | - | - | - | - | - | - | - | 2 | 2 |

| Таблица преобразуване на странициза програма D | ||||||||||||||||

| D0 | - | - | - | 0 | 0 | 0 | - | 1 | 1 | 1 | - | - | - | - | - | - |

| 1 | - | - | - | - | - | - | - | - | - | - | 1 | 1 | 1 | 1 | 1 | 1 |

Ако всяка страница има обем от 1000 адресируеми клетки, тогава, например, в цикъл 9, достъп до виртуален адрес 1100 програма А ( виртуална страница 1, отместването на страницата е 100) ще доведе до извикване на физически адрес 2100 ( физическа страница 2, изместване навътре физическа страницасъщото като във виртуалния, тоест 100).

Нека сега разгледаме приложението на тези общи принципи превод на адрес на страница V микропроцесорс архитектура IA-32 с размер на страницата 4 KB.

база преобразуване на странициобслужва 32-битов линеен адрес, получени на етапа на трансформация на сегмента логичен адрес. Преобразуване на странициизпълнява се, когато стойността на PG бит = 1 в контролния регистър CR0.

В този случай най-високите 20 бита линеен адресвсъщност представляват число виртуална страница. Въпреки това, с директно едноетапно преобразуване на това число в числото физическа страницанеобходима е таблица от 2 20 елемента, всеки с дължина 4 байта (20-битов номер на страница плюс допълнителна информация), т.е. 4 MB. В мултипрограмна среда такава таблица може да се изисква за всяка задача. Тази таблица трябва да се съхранява постоянно в RAM, за да не се увеличи значително времето за формиране физически адрес. За тези цели ще е необходимо постоянно да се резервира значителна част от капацитета на RAM, което беше практически невъзможно на етапа на появата на първите MP-базирани компютри с архитектура IA-32.

Вместо това микропроцесорът използва двустепенен превод на адрес на страница. Основната страница, наречена директория с таблици на страници(KTS), съдържа 1024 32-битови таблица на страници елемент директория(ECTS - Запис в директория на PDE страници). Всеки от тях се обръща към подчинен таблица на страниците(TS), т.е. разрешени са общо до 1024 подчинени таблицистраници. Всяка таблица на страници съдържа 1024 32-битови елемент на таблицата на страницата(ETS - PTE страница влизане в таблица), всяка от които адресира физическа страница. Така общият брой адреси физически страницие равно на 2 20, тоест всичко е виртуално адресно пространство(4 KB * 2 20 елемента = 2 32 байта). Всяка таблица заема 1024 * 4 = 4 KB, тоест точно 1 страница. Общ размер на таблиците, използвани за преобразуване на страници, не намаля, а дори леко се увеличи поради използването на директорията на таблицата на страниците. Въпреки това, първо, почти винаги в една система този размер може да бъде значително намален поради факта, че някои линейни адресиникога няма да се формира (и тази информация е дадена дескрипторни таблицисегменти) и не е необходимо да създавате таблица на страници за тях. И второ, само таблица на страници директория и таблица на странициизпълнявана в момента програма. Почивка таблици на страницитеможе временно да се съхранява във външна памет.

Ориз. 3.13.

Така преобразуването на линеен адрес във физически има формата, показана на фиг. 3.13.

Горните 20 цифри линеен адрессе разделят на две 10-битови полета: поле таблица на страници номера на каталожни позициии поле номера на елементите на таблицата на страниците. От директория с таблици на страници, и всеки таблица на страницитезаемат точно 1 страница и са подравнени към границата на страницата, тогава долните 12 бита от основния им адрес са нула и за определяне на техните физически адресДостатъчно е 20-битово поле.

За директория с таблици на страницинеговият 20-битов адрес е вътре контролен регистър CR3. CTS е постоянно в паметта и не участва в размяната.

Горните 20 цифри физически адрес таблици на страницитеса извлечени от СТЕ. Структурите на елемента CTS и елемента TS са подобни (фиг. 3.14).

Ориз. 3.14.

Най-значимите 20 бита на елемента дават основния адрес таблици на страниците(в ECTS) или физическа страница(в ETS). Битовете P, A, R/W и U/S имат определени прилики с тези на сегментния дескриптор; други битове имат специфични цели.